# Adiabatic Technique Usage for the Analysis of Power Dissipation in Logic Gates

# Ch Vijayhalakshmi<sup>1</sup>, Dr. Jaikaran Singh<sup>2</sup>

<sup>1</sup>Research Scholar, Department of ECE, School of Engineering, LNCT University Bhopal MP India <sup>2</sup>Professor Department of ECE, School of Engineering, LNCT University Bhopal MP India

vijji.lnctphd@gmail.com1, jksingh81@gmail.com2

Article History: Received: 11 January 2021; Revised: 12 February 2021; Accepted: 27 March 2021; Published online: 16 May 2021

Abstract: Adiabatic circuits are low power circuits, which oversees the reversible method of reasoning that it stores the power and gives it back again. At present Several Adiabatic methodologies have been gotten for viable power dispersal. The system used to restrain control dispersing are Efficient Charge Recovery Logic, Positive Feedback Adiabatic Logic, and Pass Transistor Logic. The Adiabatic method is essentially cast-off for decreasing the influence dissipating in VLSI tracks, which does indict and squaring system. The method of reasoning doors accepts a critical activity in various number shuffling assignments, for instance, the twisted, multiplier, divider and processors. To compile the power spread, a profitable full adder proposed for the particular adiabatic methods, and all of the circuits have been simulated by 25nm innovation utilizing the tanner EDA tool.

## Keywords: Adiabatic logic, low power dissipation, Efficient Charge Recovery Logic, Positive Feedback

## Adiabatic Logic, Pass Transistor Logic, low power adder.

## 1. Introduction

Recently power dispatch issue for designing the VLSI circuits. Most of the electronic contraptions rely on the low power circuit structure. To overcome the essentialness recovery rule introduced, and it is known as an adiabatic basis. This circuit is which the imperativeness is reused back to edge voltage, and no essentialness is wasted [1], and it in like manner gives the expanding cost of imperativeness, less control use, and augmentation in affectability. The essential objective of the low power circuit is that it increases battery life, decreases the size, weight, and the cost of the contraptions and diminishes the unconventionality in quick devices. In cutting edge circuits the power scattering can be diminished by using a couple of adiabatic methods of reasoning. Adiabatic circuits use 'Reversible reason' to safeguard imperativeness. It works with trading practices, which diminishes the power, by giving the set away imperativeness back to the stock, so the power dispersing is reduced [2]. Adiabatic method of reasoning achieves low control and snappier action. So the general standards are adopted by the Adiabatic methodologies are (1) Never switch ON a transistor when voltage is given from source to drain and (2) Never mood killer a transistor when present trips through the track.

Entryways are the central structure squares of any circuit in which it is expected to perform a quick number shuffling movement. Likewise, they are the most vital justification modules used in the arrangement of electronic VLSI circuits. It plays out the explanation behind all figuring's, for instance, expanding, counting and separating, etc. In entirety to finishing the obligations of extension, the snake goes before the hotspot for a few, inconvenient circuits like the multipliers, subtractors, RAMs, report estimations, and knowingly extra.

## 2. Adiabatic logic

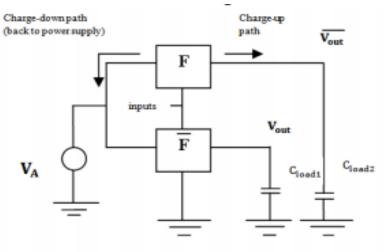

The expression "adiabatic" alludes to the thermodynamic system that doesn't exchange imperativeness with the external condition, and like this, there is no proportion of force or essentialness is scattered. In this framework during, the trading process, this justification diminishes the dissipating of force or essentialness and keeping in mind that it reuses the imperativeness by reusing it from the stack capacitance, with the objective that a comparative imperativeness can utilize for next movement. The Fig.1 exhibits that the method wherein changeover occurs without imperativeness being either lost or gotten from the structure instead of warmth or electronic charge is essential. This way, an ideal adiabatic method of reasoning would work without the addition or decay of electronic charge.

This reason gives a way to deal with reuse the essentialness set away in trouble capacitors than differentiating the ordinary strategy for discharging the load capacitors to the ground as opposed to wasting the imperativeness [3]. In any case, the charge which is grounded can be reused back and accommodates the power clock.

# Fig.1. Adiabatic logic

In low control, VLSI circuits are arranged by using a couple of adiabatic frameworks, for instance, capable charge recovery method of reasoning, positive analysis adiabatic justification, and pass transistor basis.

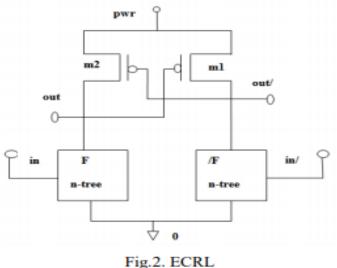

### 3. Efficient charge recovery logic (ecrl)

ECRL gives another procedure that performs precharge and appraisal, all the while where it gets rid of the precharge diode and scatters the less essentialness when appeared differently concerning the next adiabatic circuits [4]. It contains a cross-coupled PMOS transistors and two NMOS transistors in N-helpful square which is reproduced by using two cross-coupled transistors M1 and M2 as showed up in the Fig.2. In light of the action of cross couple PMOS transistors, a Full Swing Output is captured in both pre-charge and recovery stages.

It works with a four-phase power clock subject to the Evaluation, Holds, Recover, and Wait for movement. This clockworks capably to recover the charge passed on by the store clock. Each historical of the timepiece is trailed by the accompanying dated of the timer with a  $90^{\circ}$  stage slack. So when the last stage is in the hold organize, the accompanying stage must be surveyed by the basis regards in the precharge and evaluation process [5].

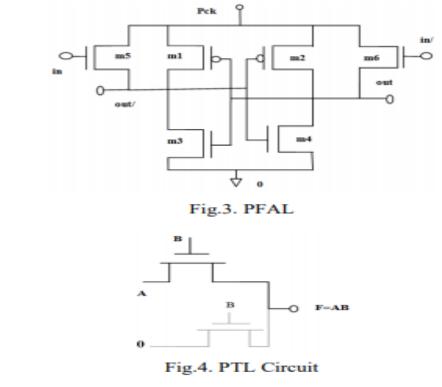

#### . Positive feedback adiabatic logic (pfal)

The PFAL is a partial imperativeness recovery circuit with twofold rail sort out. To keep up a vital good way from a method of reasoning level debasement on the yield center points PFAL entryway with an attach made of two PMOS transistor M1, M2, and two NMOS transistors M3, M4 are used. Both transistors create two enhanced yields. A four-phase power clock is generally known as time contrasting source. Which can be used for adiabatic charging reason [6]? Right, when the data is high the estimation of power clock grows which achieves the transistors M5 and M1 to be in ON state. Due to this method the out is related to the ground and/out will be established on the movements of power clock. Right when the power clock comes to, out will end up zero just as out will be gone to Vdd, which will go about as a commitment for the accompanying period of the movement.

Allow us to consider the power clock shifts from Vdd to 0 then the imperativeness will be recovered through the transistor M1. The useful squares of Fig.3 are related to parallel with the PMOSFET of an adiabatic speaker, and this way, it is made with a transmission entryway process. The two F trees are recognized by using the method of reasoning components of PFAL, and it is moreover used to create positive and negative yield swings [7].

Pass

## **TRANSISTOR LOGIC (PTL)**

Pass transistor method of reasoning is one of the sorts of without a doubt comprehended NMOS justification style. In the Integrated circuit structure, it uses a couple of method of reasoning families. It reduces the transistor look at by taking the overabundance transistors, which is used to make various reasons entryways. Right when diverged from indispensable CMOS justification, PTL uses least transistors, fast, and requires low control. In another method of reasoning family's data is associated with the portal terminal of transistor anyway in PTL. It is in like manner associated with the source or channel terminal of the transistor, as showed up in Fig.4. When using this as a pass transistor, the contraption may lead current in either heading of the device.

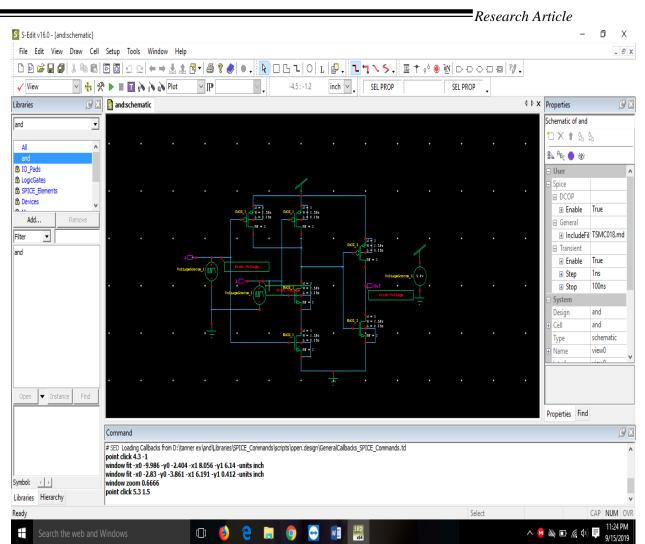

#### Circuit implementation of adiabatic techniques using and gate

In the ECRL framework, a power clock signs isolated into four phases: delay, evaluate, hold, and recover. During hold up organize, a data sign is set up by the past method of reasoning portals. During the survey organize, an information sign is kept stable, and the door yields are resolved reliant on the enduring banner. During hold organize, a stock voltage is kept steady to VDD, and the information sign is lessened. During recover organize, a coordinated VDD advances toward getting to be lower, and the imperativeness from the yield center points is reused during the discharging system. Hereafter, the yields from the past stage are used as a commitment for the present stage, and they are synchronized using the times of the clock cycle.

## 5. Results and conclusion

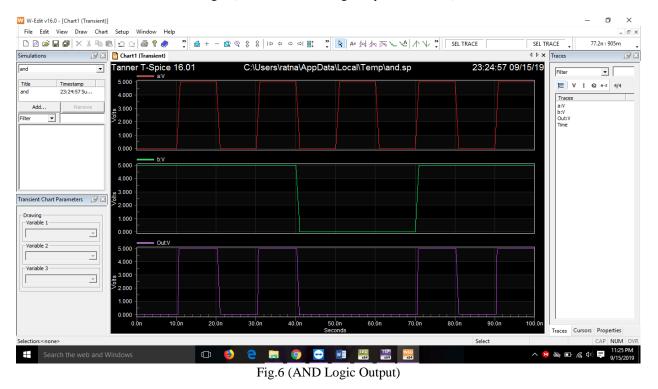

Fig.5 (Schematic of AND gate by fixed CMOS)

Research Article Power Power Results VVoltageSource 1 from time 0 to 100 Average power consumed -> 6.381695e-015 watts Max power 4.971481e-004 at time 7.08044e-008 Min power 0.000000e+000 at time 0 51 o 2 See 122 . 58 m 2 5 m 21

Fig.7 (Schematic of AND gate by Adiabatic Logic)

٦.

**POWER RESULTS**

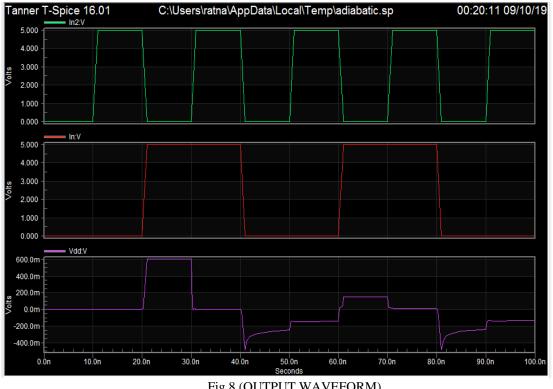

Fig.8 (OUTPUT WAVEFORM)

Time

```

Power Results

VVoltageSource_1 from time 0 to 100

Average power consumed -> 9.795540e-016 watts

Max power 2.043998e-004 at time 6.08416e-008

Min power 0.000000e+000 at time 0

0.01 seconds

Parsing

Setup

0.01 seconds

DC operating point

0.03 seconds

Transient Analysis

0.01 seconds

Overhead

0.89 seconds

Total

0.94 seconds

Area

Device and node counts:

MOSFETs -

6

MOSFET geometries -

2

Voltage sources -

2

Subcircuits -

0

Model Definitions -

2

Computed Models -

2

Independent nodes -

6

Boundary nodes -

з

Total nodes -

9

```

### Conclusion

The essential idea of this endeavor is to introduce the arrangement of world-class and power capable full snake setup using a multiplexer founded authorization transistor basis. In the present effort, the filled snake proposal is realized by dissimilar methods of reasoning like SERF, PFAL, and ECRL, etc.

Further, the structure is executed using a pass transistor justification got together with other reasons. The amount of transistors required for recognizing a mixed CMOS plan and isn't the number of transistors required in understanding the structure of and gateway using CMOS transistors openly. Along these lines, the necessary basis can be recognized inside a streamlined locale, which performs faster when appeared differently concerning the standard standing CMOS filled snake structure. "From the yield results, I found around 40% less essentialness change in adiabatic justification arrangement when appeared differently concerning the stationary CMOS structure accomplice.

#### **Future work**

ADIAMEMS: To perform the motorized technique for thinking in CMOS in an extremely adiabatic (asymptotically thermodynamically reversible) style necessitates that the premise changes be driven by a semi trapezoidal (level bested) control clock voltage waveform, which must be conveyed by a full section with high Q (quality factor). Beginning, MEMS resonators have achieved unimaginably high frequencies and Q factors and are contorting up exhaustively utilized in correspondences framework on-chip (SOC) for RF sign separating, heightening, and so on.

**APPLICATION OF NANO-TECHNOLOGY**: Carbon nano-tubes created using Chemical Vapor Deposition (CVD) can be picked to conform to a spiraling shape. As such, an incredible superiority issue Q container is to be practiced. The work left is to be practiced for this arrangement would fuse a methodology for making it keep its structure since nano-tubes are regularly not unyielding. Similarly, setting the chamber to use in a circuit would cut down the suitable Q as a result of the crossing point discontinuities.

**<u>SPACECRAFT</u>**: The amazing cost per-weight of driving figuring related power supplies, sun fueled sheets, and cooling structures into space powers an enthusiasm for adiabatic power decline in transport in which these sections check a basic piece of hard and fast rocket weight.

#### References

Research Article

- 1. S. G. Younis and T. Knight, Practical Implementation of Charge Recovering Asymptotically Zero Power CMOS", Proc. of 1993 Symposium on Integrated Systems, 234-250. MIT Press (1993).

- 2. A. G. Dickinson and J. S. Denker, Adiabatic Dynamic Logic", Proceeding of the Custom Integrated Circuits Conference. IEEE (1994).

- 3. low power design methodologies Jan.M.Rabey and Massoud Pedram Kluwer academic publishers

- A. G. Dickinson and J. S. Denker, "Adiabatic dynamic logic", IEEEJ. Solid-State Circuits, Vol. 30, pp. 311-315, March 1995.

- Prof Mukesh Tiwari, Prof Jaikaran Singh, Mr Yashasvi Vaidhya "Adiabatic Improved Efficient Charge Recovery Logic for low power CMOS logic " International journal of Electronic Communication and Computer Engineering pp 350-354 Vol 1 issue 5.

- Samik Samanta Power Efficient VLSI Inverter Design using Adiabatic Logic and Estimation of Power dissipation using VLSI-EDA Tool Special Issue of IJCCT Vol. 2 Issue 2, 3, 4; 2010 for International Conference [ICCT-2010], 3rd-5th December 2010

- Prasad D Khandekar, Shaila Subbaraman, and Abhijit V. Chitre Implementation and Analysis of Quasi-Adiabatic Inverters International conference of engineers and computer Scientist 2010 Vol II IMECS 17-19-201 Hong Kong

- 8. A. Kishore Kumar, D. Somasundareswari, V. Duraisamy, T. Shunbaga Pradeepa Design of Low Power Full Adder using Asynchronous Adiabatic Logic European Journal of Scientific Research Vol.63 No.3 (2011), pp. 358-367

- 9. Aiyappan Natarajan, David Jasinski, Wayne Burleson, Russell Tessier A Hybrid Adiabatic Content Addressable Memory for Ultra Low-Power Applications GLSVLSI'03, April 28–29, 2003, Washington, DC, USA

- Jianping Hu, Lv Yu P-type Adiabatic Computing Based on Dual-Threshold CMOS and Gate-Length Biasing Techniques Journal of Convergence Information Technology(JCIT) Volume7, Number6, April 2012 issue 6.19

- Byong-Deok Choi, Kyung Eun Kim, Ki-Seok Chung, and Dong Kyue Kim "Symmetric Adiabatic Logic Circuits against Differential Power Analysis " ETRI Journal, Volume 32, Number 1, February 2010