Research Article

# FPGA Implementation of Proficient 16-Tap FIR Filter Design Using Decision Tree Algorithm

# A Murali<sup>1\*</sup>, K Hari Kishore<sup>2</sup>

<sup>1,2</sup>Department of ECE, Koneru Lakshmaiah Education Foundation, Vaddeswaram, Guntur, A.P, India <sup>1\*</sup>amurali3@gmail.com

Article History: Received: 11 January 2021; Accepted: 27 February 2021; Published online: 5 April 2021

**Abstract:**Lately, channel is one of the key components in signal handling applications. Among different channels, Finite Impulse Response (FIR) channel is broadly utilized in Digital Signal Processing (DSP) applications for shifting/denoising. For enormous scope coordination (VLSI) execution of fixed-coefficient FIR channels, huge asset used customary multipliers that can be acknowledged by a solitary steady multiplication (SCM) and numerous consistent augmentations (MCM) square utilizing movement and include/take away tasks. For a proficient execution, a variable size apportioning approach is proposed in direct structure channel structure that devours less zone and 11% of decrease in basic way delay, 40% decrease of all out force utilization, 15% decrease of zone delay product(ADP), 52% decrease of vitality delay product(EDP), and 42% decrease of intensity territory product(PAP), on a normal, over the cutting edge techniques. In this paper, a state choice tree calculation is proposed to decrease unpredictability in channel tap cells of variable size apportioning approach. The proposed plot creates a choice tree to perform move and expansion/deduction and aggregation dependent on the consolidated SCM/MCM approach. This plan diminishes the quantity of postpone registers required for tab cells. The proposed snake design will be actualized in Xilinx Zed, Spartan and Virtex devices and Area, power and speed investigation will be performed.

Keywords: FIR Filter, Power Area Product, SCM, MCM

## 1. Introduction

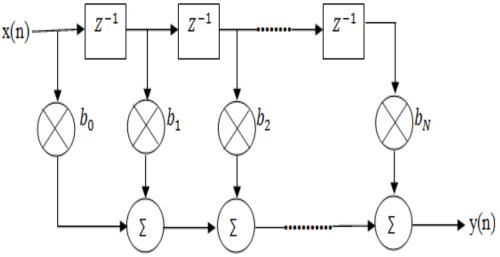

The filtering cycle is one of the most fundamental activity in Digital signal processing applications, for example, Audio handling, wired/remote correspondence, Image &video preparing designs [1]. Structure for low unpredictability, low force and effective FIR channels has been raised as a significant examination zone for the last four decades [2]. Computerized channels assume an imperative job in DSP applications because of their unprecedented presentation in separating/de-noising in cell phones, TV, Internet and so forth. Which are the key reasons that Digital channel has become significance in human life? When all is said in done, Filters are utilized for signal partition and rebuilding from loud sources sent through channel. Signal extraction must requires when sign has been endured with obstruction, clamor or different signs source displays with unique sign. This issue can be occurs on either simple signs or advanced signs transmission. Simple channels are fast, cheap underway and measure the sign that has interfered with clamor in both frequency and abundancy though advanced channels measures different sorts of signs with various recurrence range and bandwidth. For simple channels, significant boundary contemplations are needed to look after exactness, working extent and security of the resistors and capacitors. Interestingly, advanced channels are having better execution in look after precision, solidness and reclamation with minimal equipment use. The limitations movements to the properties of the corrupted signs and the hypothetical issues related their preparing [3]. For better Filter execution advancement regarding region, power utilization and deferral can be accomplished by various increase procedures i.e. Shift and add (SA) multiplier and Wallace tree multiplier can be utilized for coefficient duplication. Wave convey adder(RCA), Brent Kung adder(BKA), Kogge Stone adder(KSA), Ladner Fischer adder(LFA) and Han Carlson adder(HCA) are investigated for ideal execution for additional utilization in different augmentation and aggregation methods [4].The fixed coefficient FIR is planned with Multiple Constant Multiplication (MCM) conspire. The computational investigation demonstrated that rendered type of the FIR channel and induction of stream chart has decreased register intricacy. However, the numerical investigation is mind boggling for MCM conspire [5]. The 4-tap equal FIR channel utilizing Virtex-5 FPGA is coded in VHDL utilizing top-down various leveled plan. The plan devours a little territory out of the whole FPGA land leaving a lot of assets for other equal processors on a similar gadget [6]. An exact examination and improvement of basic way for rendered direct from (RDF) FIR channels is assessed by looking at the postponement of a tap and comparing deferral of the coefficient duplication just [7]. A large portion of the exploration on plan and usage of FIR channel so far spotlight on the advancement of MCM squares [8], [9].But it is seen that the item aggregation area often contributes the significant aspect of the basic way, with the end goal that the circumstance enhancement of MCM square doesn't affect altogether on the general speedup of the FIR channels and mistake versatile strategies for voltage scaling [10]. The general structure of the filter is shown in figure 1. It has delay, multipliers and adder elements. Multiplier design on FPGA hardware requires more area as the design complexity is more and needs large resources resulting in high cost.

Figure 1. General structure of FIR filter

A definite unpredictability analysis of the equipment and time consumed by each section of a move to prepare an efficient crossover structure FIR channel, including dependent mixture structure channels, also leads to a troubling increase in Shift Add and register complexities in the SAB.Thus, a variable size apportioning approach for productive execution of straight stage FIR channels utilizing Decision Tree Generation calculation.

The remainder of the paper is sorted out as follows: Literature survey of the current strategies is appeared in segment 2. The proposed variable size dividing approach is talked about in segment 3. Results and discussion is given in segment 4. Conclusion and future scope is provided in section 5.

#### 2. Literature Survey

With the aid of Xilinx device generator software, P.C. Bhaskar et al. [11]proposed a finite impulse response filter using distributed arithmetic based on FPGA. The structure generates a good signal-to-noise ratio and a low mean square error. Chip signal interference and high heat dissipation can be minimised to a greater degree.

By synthesizing the filter coefficients to optimize the price savings of the TDA block, Jiajia bird genus et al. [12] have enforced a brand new style methodology for area-power economical FIR filter implementation. So as to decrease the sizes of later structural adders and registers while not violating the filtering needs, this block relies on quantity division at any best faucet position. Retiming or relocating the structural adders and registers will improve the turnout and reduced the implementation price of the multiple constant multiplication blocks.

Ahmed Liacha et al. [13] has proposed area aspect of RADIX-  $2^r$  is confronted to area efficient algorithms, notably to the cumulative benefit heuristic (Hcub) known for its lowest adder-cost. RADIX-2 is one of the most common MCM heuristics. RADIX-  $2^r$  achieves the best results in speed, power, and area, particularly in MCM blocks of high complexity, with a simple recoding and minimal computational effort.

A low-power adaptive FIR filter architecture based on the DA algorithm was proposed by S. Ramanathan et al [14]. To decrease the switching operation and power consumption, the Least Mean Square (LMS) algorithm was used. For the FIR filter architecture, the DA used the carry save accumulator; in the FIR filter design, it occupied more space.

A low power and high speed 16-order FIR filter design has been proposed by Mittal et al. [15]. This method was optimised based on an approach such as the FIR filter coefficient with FIR filter input, filter field, power and delay.

A low power FIR filter design based on hybrid artificial bee colony (HABC) has been proposed by Atul Kumar et al.[16] to decrease switched power consumption. It has a higher convergence rate than a typical ant bee colony.Low-power filtering is supported by Ant Bee optimization, but it consumes more LUT/Slices.

#### 3. Proposed Methodology

Another option tree making calculation using Variable Partition Hybrid Type Structures is proposed in this paper to plan an advanced FIR channel. A MAC is the operation of duplicating a coefficient in the FIR channel structure by comparing the deferred information test and aggregating the result. For the most part, FIR channels need one MAC for every tap. The duplicate collect square in the FIR channel structure has multiplier, worm, and collector squares. When compared to current FIR Filter systems, it is possible to reduce the amount of postpone registers needed in tap cells, resulting in a substantial reduction in equipment asset use. Additionally, the deferral and force would be reduced. The channel coefficients used are fixed-point in this structure, which will minimize the multifaceted existence of truncation and measurement in Tap cells.

#### 3.1 Low Force Multiplier for FIR Filter Design

The stop band vitality of the information signal in FIR channel request changes. Low force applications required reconfigurable FIR channel auxiliary structures. In FIR networks, increases are essential tasks. The channel's heaviness, on the other hand, is relentless. Multipliers play an important role in today's advanced sign handling and other applications. In addition, the use of low force is an important problem in the layout of multipliers. It is a brilliant idea to minimize the amount of operations in this way to decrease specific force is a significant piece of full force utilization to decrease notable force utilization, so the need for quick and low force multiplier has grown. The primary emphasis of the architect is quick and low force quality. The aim of a good multiplier is to produce a unit that is truly stuffed together, fast, and low on force utilization. In various correspondence structures, the Finite-Impulse Response (FIR) channels assume a significant task. A wide variety of activities, such as noise reduction, synchronized sifting, obstacle crossing out, weakening reduction, channel balance, and so on. In general, the zone, time and force utilization of a FIR channel is overwhelmed by the unpredictability of increases. The Direct Form (DF) and made direct structure (TDF) structures are two attempts along these lines to reduce this unpredictability by using multiplier-less FIR networks.Every augmentation is acknowledged by the single consistent increase (SCM) conspire in a move and include DF channel, and the fractional items are included by a viper tree to get the final yield. In a TDF pipe, on the other hand, all the coefficients repeat the current information test, and the items are then passed through a unit delay and the simple SAB to generate the channel yield. The various consistent replication (MCM) approaches consider the increases in this scenario.

Due to rising PC and sign preparing applications, the interest of quick handling has grown. Poor force usage in the multiplier plan is also a major problem. It is a smart idea to minimize the amount of tasks in this way to decrease specific power, which is a vital part of all out force usage, so that the need for a quick and low force multiplier has increased. For the most part, the planner concentrated on the structure of rapid and low force efficient loops.

#### 3.2 Variable Size Partitioning Approach

In this study, as a fixed-size dividing (FP) approach, we use the variable size apportioning approach and the associated mixture structure channels as "FP-Hybrid" channels. In view of the examination above.

The scope of achievable qualities (2 to (N/2)) in the FP-crossover channels of the administering boundary (L) increases with the request for a channel (N). The structure options in the Fixed-pointHybrid channels are enormous because different L estimations result in different register complexities and FA's.An experimentation technique controls a specific estimate of L, and as a result, the subsequent structure for the chosen estimation of L can be far from the ideal plan.

To actualize a given coefficient range, the technique only uses fixed-size MCM squares. We see that MCM operations are not used in a proficient manner in any of these segments. For example, consider a 16-tap benchmark channel with coefficients h (n) = 2, 2, - 2, - 5, 0, 10, 8, - 12, - 26, 0, 68, 128, 128, 68,...,2, 2 and L = 2, 6 and 12. For comparative calculations of L, the fixed-size MCM allotments. The zone proficiency of the MCM square decreases as the amount of these striking coefficient increases. Since the qualities, as well as the contiguousness of the channel coefficients, are essential to the sub-structure in multiple constant multiplications square. Basic purpose of the Variable-Partition path is to remove the need to select a clear advantage of separating boundaries and restricting the unpredictability of the SA alongside the intricacy of the register. In light of the foregoing assumptions, we suggest two calculations for obtaining successful step and include dependent VP-Hybrid structure FIR channels: i) Single constant multiplication (SOVH) Variable partition hybrid (SOVH) calculation and (ii) Multiple constant multiplication situated Variable Partition -Hybrid (MOVH) calculation.

#### (i) Single constant multiplication Oriented Variable Partition-Hybrid (SOVH) path

Consider a 16-tap benchmark channel with coefficients h = 3, 6, 0, -16, -19, 12, 76, 128, 128, 128, 128, 76,...,6, 3We discovered that the majority of the variable size allotments are actualized using the SCM-arranged half breed structure FIR channel, which is centered on the proximity of two progressive coefficients. The VP-Hybrid structure of the SCM. Using the H whelp measurement, the disintegration of each section is achieved and comparing shift-include geography is seen as the information word-length to be eight-bits for the above structure model. The SCM-arranged VP-half breed structure consumes 96 DFFs in the information defer line, 50 Full Adders in the multiplier square, 115 FAs in the PSA square, 52 FAs and 50 DFFs in the SAB, while the structure consumes 8 DFFs in the information postpone line, 34 FAs in the multiplier square, 62 FAs in the PSA square, 96 FAs and 188 DFFs in the SAB. As an increase in the sharing of simple sub articulation gives an excellent decrease in the intricacy of multiplier and PSA squares in FA to upgrade the usual sharing of sub articulation depending on the proximity of the coefficients of the channel.

#### (ii) Multiple constant multiplication-Oriented Variable Partition-Hybrid (MOVH) path

For example, the boundaries of h, u, MCM(u), s(u), h and M are indistinguishable from the SOVH approach. A structure close to that used in the SOVH method, with the H-cub algorithm used to track the degree of simple sub-articulation sharing. The parcels created by the MOVH method are similar to those created by the SOVH method. Channel of the MCM-situated VP-cross breed (MOVE). The MOVH method results in a substantial reduction in the FA multifaceted design and natural fan out of the hubs in the multiplier square, reducing the channel structure's CPD. As a result, MOVH channels are well suited to the rapid use of FIR channels for a variety of requests.Note that both the methods proposed for k = 0 are comparable to the TDF structure, while k = N/2-1 generates a DF structure. To illustrate, let us consider a 7-tap benchmark channel with a  $h(n) = \{-1, 0, 9, 16, 9, 0, -1 \text{ coefficient set includes only the critical objectives of cost-0 (1, 0, 16) and cost-1 (9) for this situation. We have <math>k = N/21 = 3$  because there is no usual sub-articulation sharing among the objective basics, and therefore both the proposed plans for the above structure model result in a DF structure.

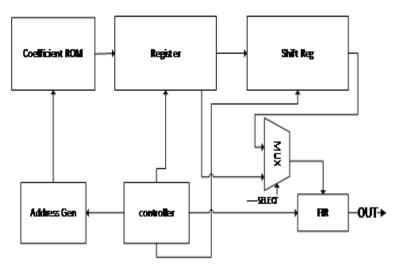

Figure 2.Designed Architecture of DTG-FIR filter

The Figure 2, clarifies the general proposed engineering. The regulator is limited by the position generator, log, FIR and Shift register. FIR and output to register and transfer register are supported with one contribution from MUX.

For each tap on a FIR channel, one MAC unit is typically needed. The layout of the FIR channel includes the multiplier, viper and gather squares of the increased gather square itself. In this approach, fewer deferred registers needed in tap cells are feasible, which can fully reduce the use of equipment assets and, in comparison to the current FIR filter designs, the delay and force would decrease. The channel coefficients used are fixed-point in this structure, which will reduce the unpredictability of truncation and measurement in Tap cells. Consider a 16-tap benchmark channel with a fixed coefficient of  $h = \{3, 6, 0, -16, -19, 12, 76, 128, 128, 76... 6, 3\}$ . These coefficients are stacked into a 16-bit coefficient ROM. The regulator unit will manage the log, and a shift-based option tree will be generated based on the number of movements, and will include activities such as duplication and gathering in order to perform separating. Guidance from the selection tree unit will be stacked for each cycle to determine the number of halfway postpone registers between tap cells and utilizations choice tree to execute tap cell activity. This suggested approach will preserve a strategic distance to conduct tap cell operation from the number of halfway postpone registers between tap cells and utilizations choice tree to execute tap cell activity. This suggested approach will preserve a strategic distance to conduct tap cell operation from the number of halfway postpone registers between tap cells and use option tree. In Xilinx ISE, this suggested design will be revised and tested in FPGA devices for Xilinx Virtex6/7, Spartran6 and Zynq-7000.

## 3.3 Working guideline of proposed calculation

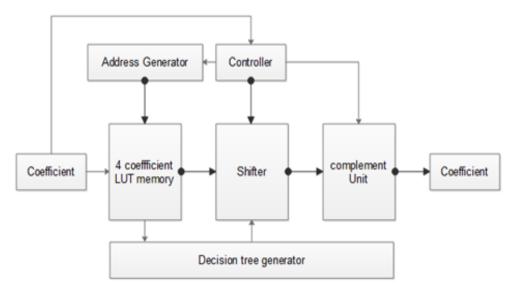

The exorbitant multipliers are avoided in the FIR structure by using LUT-based SCM/MCM-based computerized equipment in previous exploration. As indicated by the factor segment algorithm, the LUT-based FIR channel stores coefficients in ROM, and SCM/MCM-based move and expansion is acted in every tab cell (VPA). The streamlining of the LUT for channel coefficient, which impacts the zone cost of number-crunching units and registers, has been an important structural problem in the past study. The Decision Tree Generation Algorithm (DTGA) is known to reduce the LUT size to 40 percent of the normal LUT in the VP approach in this analysis. In Figure.3, shows the outline of DTGA based FIR channel structure by utilizing coefficient LUT advancement procedures.

Figure 3. Block diagram of the Coefficient LUT

This section discusses the Decision Tree Generation algorithm technique for optimising LUT memory with a VP- FIR filter. Centred on the 16 tap direct form structure, the architecture is implemented.

Table 1. General 16-bit Coefficient LUT table for 16tap

| Address(C1) | Coefficient(C2) | Address(C3) | Coefficient(C4) |

|-------------|-----------------|-------------|-----------------|

| 0000        | А               | 1000        | 15A             |

| 0001        | 2A              | 1001        | 14A             |

| 0010        | 3A              | 1010        | 13A             |

| 0011        | 4A              | 1011        | 12A             |

| 0100        | SА              | 1100        | 11A             |

| 0101        | 6A              | 1101        | 10A             |

| 0110        | 7A              | 1110        | 9A              |

| 0111        | 8A              | 1111        | 16A             |

Table 2. Decision Tree for Variable partition FIR

| ROM<br>Address | Coefficient(C1) | No of shifts | Result       |

|----------------|-----------------|--------------|--------------|

| 0000           | 1 x A           | 0001 <<1     | 2 x A(SCM)   |

|                |                 | 0001 <<2     | 4 x A(SCM)   |

|                |                 | 0001 <<3     | 8 x A(SCM)   |

|                |                 | 0001 <<4     | 16 x A(SCM)  |

| 0010           | 3A              | 0011 <<1     | 6A(SCMMCM)   |

|                |                 | 0011 <<2     | 12A(SCM/MCM) |

| 0100           | 5A              | 0101 ≪1      | 10A(SCM/MCM) |

| 011 0          | '/A             | 0111≪1       | 14A(SCM/MCM) |

The VP-FIR channel request of 16 coefficients is organized in Table.1. Clearly the twos supplement of the factor in the C2 segment of relating lines can be utilized to assess every coefficient in the 4th segment (C4) of Table one. The two is supplemented by any factor showing negative mirror balance aside from 8A and 16A on the second segment of a similar line. The LUT size is decreased dependent on the evenness property of the coefficients of the relative multitude of two sections depicted previously. It is conceivable to deliver a capacity coefficient of C4 from C2. In Table two, just four odd-position factors are put away in the LUT memory. By moving 1A, 6A from 3A, and 10A from 5A, the coefficients 2A, 4A, 8A, and 16A can be created. The 16 number of put away LUTs by the technique is diminished to 4-Look up table memory. In this technique, a decrease of 16 put away look up table numbers to 4-look up table memory is given. SCM is utilized if the coefficients. From past work, it is discovered that the proposed FIR configuration dependent on DTA requires a territory decrease tantamount to existing work.

The output waveform configuration of the DTG FIR filter is shown in Figure.8. The correctness of the suggested configuration of the DTG FIR filter validates the correctness of the design. In RAM, the value signal is produced at random, which is multiplied by the coefficient. The shift and add technique is used in the DTG- FIR filter to perform FIR filter operations instead of the usual multiplier. The input data for the filter is multiplied with the filter coefficient. The value that gives the initial cycle value and is stored with the accumulator in the y register includes a zero value that is applied to the y. The accumulator of the clock cycle is used to store the result. Optimizing the LUT via the Decision Tree Generation algorithm reduces the total filter area. The RTL view of the FIR filter design proposed is shown in the figure. 9.

## 4. Results and Discussions

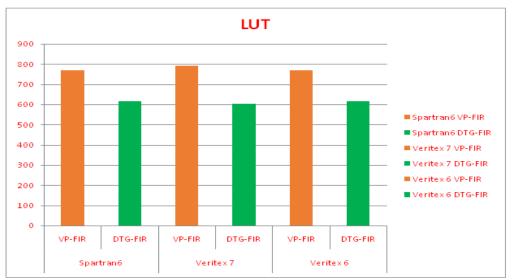

In the Xilinx tool, the VP shift and add dependent FIR filter with LUT optimization technique is implemented by using Verilog code and checked by analyzing field, power, delay, which is tabulated in table 3, with various devices such as Virtex-6, Virtex-7 and Spartran-6 devices.

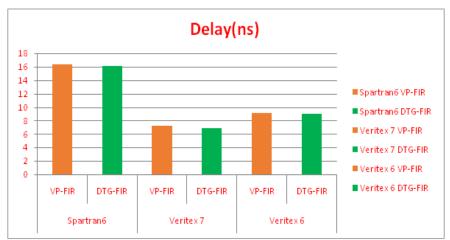

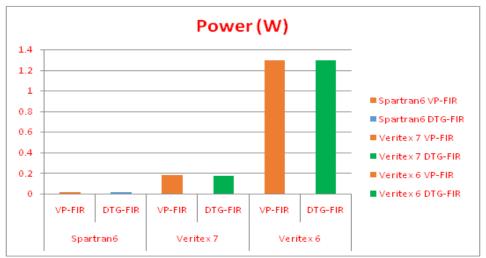

For a tap of 16 taps, the efficiency of the LUT optimized FIR filter is evaluated. The comparison graph of the LUT, Delay, and Power output for VP-FIR and DTG-FIR based on Virtex-6/7 and Spartan6 is shown in Figures 4, 5, and 6. These figures clearly demonstrate that less area has been occupied by the proposed FIR filter design, which means that the amount of FPGA output is decreased compared to the current FIR filter design.

| Device           | Methodology      | LUT        | Flip flop  | Delay(ns) | Freq(MHz) | Power(W) |

|------------------|------------------|------------|------------|-----------|-----------|----------|

| Spartran6        | Proposed-DTG-FIR | 616/5720   | 287/11440  | 16.062    | 62.257    | 0.014    |

| 6slx9-tqg144     | Existing-VP-FIR  | 771/5720   | 487/11440  | 16.324    | 61.26     | 0.018    |

| Virtex 7         | Proposed-DTG-FIR | 605/204000 | 287/408000 | 6.88      | 145.26    | 0.177    |

| 7vx330tffg1157   | Existing-VP-FIR  | 793/204000 | 486/408000 | 7.22      | 138.35    | 0.180    |

| Virtex 6         | Proposed-DTG-FIR | 617/46560  | 287/93120  | 8.992     | 111.21    | 1.293    |

| xc6vcx75t-1ff484 | Existing-VP-FIR  | 768/46560  | 486/93120  | 9.143     | 109.367   | 1.293    |

**Table3.**Performance of the FPGA for current and proposed-FIR filter design

Figure 4.LUT comparisons of synthesized for conventional and DTG -FIR filter designs

Figure5. Delay comparisons of synthesized for conventional and DTG -FIR filter designs

Figure 6. Power comparisons of synthesized for conventional and DTG -FIR filter designs

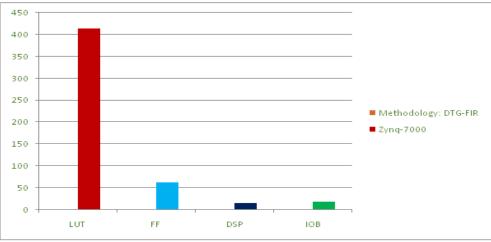

The proposed approach is implemented and tested with the Zynq 7000 hardware board using Xilinx Vivado. The use of the built 16-TAP DTG FIR filter by the Zynq hardware system on FPGA is shown in table four. It is observed that the architecture uses 62 FFs and 414 LUTs with 19 IOBs.

For the 16 taps of the DTG FIR filter based on Zynq-7000 shown in figure 7, the output of the LUT, FF with IOB optimized FIR filter is analyzed.

Table4. FPGA efficiency Architecture of the proposedDTG-FIR filter using Zynq-7000

| Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|

| LUT      | 414         | 17600     | 2.35          |

| FF       | 62          | 35200     | 0.18          |

| DSP      | 16          | 80        | 20.00         |

| IO       | 19          | 100       | 19.00         |

| BUFG     | 1           | 32        | 3.13          |

Utilization - Post-Implementation

Figure7. Design utilization for the 16-TAP DTG FIR Filter for ZYNQ-7000-3PQ208

| FIR_TOP/dk          | St1              | <u>ا کولاولاولا ولاولاولاولاولا</u>     |

|---------------------|------------------|-----------------------------------------|

| FIR_TOP/rst         | St0              | ومقدعا وقي المقدما مقدها                |

| _FIR_TOP/enable     | St1              |                                         |

| _FIR_TOP/signal_in  | 00101010         | 00 1D 10 10                             |

| _FIR_TOP/desired_in | 0000000101010110 | 0000000 10 10 10 1 10                   |

| FIR_TOP/signal_out  | 0000000011000000 | 00 100 100 100 100 100 100 100 1        |

| FIR_TOP/            | 16               | 16                                      |

| FIR_TOP/apc1        | 0000001010       | 0000000110 00 00 0000001010             |

| _FIR_TOP/apc2       | 0000000110       | 0000000110 000000101000000110           |

| FIR_TOP/apc3        | 0000001010       | 0000000110 00 00 0000001010             |

| FIR_TOP/apc4        | 0000000110       | 0000000110                              |

| _FIR_TOP/tap_set_0  | 0111110110110000 | 111 )11 111 )00 10 1 )10 [11 )00 )      |

| _FIR_TOP/tap_set_1  | 0111111001100000 | [11]11]11]00]0]]10]11]00]               |

| FIR_TOP/tap_set_2   | 0111111000010000 | [11]11]11]00]0]]11[11]00]               |

| _FIR_TOP/tap_set_3  | 0111110111000000 | [11]11]11]00 [0]]11[11]00]              |

| _FIR_TOP/tap_1_de   | 0011000110011010 | 0000000)11 111 100 101 [10 111 ]        |

| FIR TOP/tan 2 de    | 0011001010001010 | aaabaa Yuu Tuu Yuu Taa Yau Tua, Yuu 1 🎽 |

| Now                 | 1400 ps          | 1000 c s                                |

| Cursor 1            | 1041 ps          | 1041 ps                                 |

| •                   |                  | 4 D                                     |

Figure 8. DTG-FIR filter designSimulation.

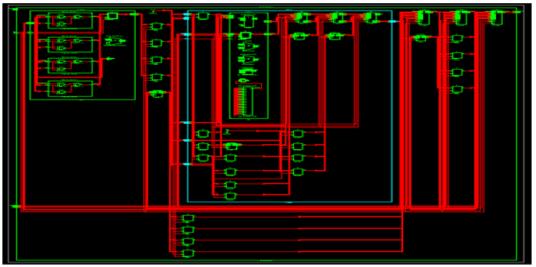

Figure9. RTL schematic of DTG-FIR filter

## 5. Conclusion and Future Scope

The design of a low-force, low-region, and fast FIR channel is a challenging and time-consuming job for DSP applications. The presentation enhancement of the FIR channel was completed in previous exploration by using variable administered Single constant multiplication/Multiple constant multiplication that provides rapid and less region design. A novel technique called option Decision tree age calculation is proposed to use symmetric and

moving property of factor in Look up table memory in this exploration, alongside VP FIR channel. Using Verilog HDL, the proposed DECISION TREE ALGORITHM FIR channel was developed in the FPGA Xilinx apparatus. The proposed approach reduced the overall LUT memory size where only four look up table stockpiling coefficients are required to structure 16 tap Fir channels. In light of LUT enhancement, the proposed FIR channel tends to be a lot more appropriate for DSP applications. The proposed version used on the Xilinx Zed board was 62 FFs and 414 LUTs with 19 IOBs. In future work, the FIR channel is designed to defeat testing uncertainty and to recover blunder rationale with troubleshooting architecture.

## References

- P. K. Rao, M. S. Begum, And C. S. Rajesh, "Utilization Of Wallace Tree Multiplier In The Design Of Scalable Microprogrammed Fir Filter Architectures," Journal Of Engineering Research And Application, Vol. 7, No. 8, Pp. 59-63, 2017.

- 3. Chen, J., Tan, J., Chang, C.H. And Feng, F., 2017. A new cost-aware sensitivity-driven algorithm for the design of fir filters. Ieee transactions on circuits and systems i: regular papers, 64(6), Pp.1588-1598.

- 4. Smith, S.W.: 'The Scientist And Engineer's Guide To Digital Signal Processing' (California Technical Publishing, San Diego, California, 1999, 2nd EdN)

- 5. Mittal, A., Nandi, A. And Yadav, D., 2017. Comparative Study Of 16-Order Fir Filter Design Using Different Multiplication Techniques. Iet Circuits, Devices & Systems, 11(3), Pp.196-200.

- 6. B. K. Mohanty, And P. K. Meher, "A High-Performance Fir Filter Architecture For Fixed And Reconfigurable Applications," Ieee Transactions On Very Large Scale Integration (Vlsi) Systems, Vol. 24, No. 2, Pp. 444-452, 2016.

- Qasim, S.M. And Bensaleh, M.S., 2014. Hardware Implementation Of Microprogrammed Controller Based Digital Fir Filter. In Iaeng Transactions On Engineering Technologies (Pp. 29-40). Springer, Dordrecht.

- Lou, X., Yu, Y.J. And Meher, P.K., 2016. Analysis And Optimization Of Product-Accumulation Section For Efficient Implementation Of Fir Filters. Ieee Transactions On Circuits And Systems I: Regular Papers, 63(10), Pp.1701-1713.

- 9. Ye, W.B. And Yu, Y.J., 2014. Bit-Level Multiplierless Fir Filter Optimization Incorporating Sparse Filter Technique. Ieee Transactions On Circuits And Systems I: Regular Papers, 61(11), Pp.3206-3215.

- Ye, W.B. And Yu, Y.J., 2015. Two-Step Optimization Approach For The Design Of Multiplierless Linear-Phase Fir Filters. Ieee Transactions On Circuits And Systems I: Regular Papers, 62(5), Pp.1279-1287.

- Y. Huang, M. Li, C. S. Li, D. Peter, And L. V. D. Perre, "Computation Skip Error Mitigation Scheme For Power Supply Voltage Scaling In Recursive Applications," J. Signal Process. Syst., Vol. 84, No. 3, Pp. 413–424, 2016.

- 12. Bhaskar, P.C. And Uplane, M.D., 2016. High Frequency Electromyogram Noise Removal From Electrocardiogram Using Fir Low Pass Filter Based On Fpga. Procedia Technology, 25, Pp.497-504.

- 13. Jiajia Chen, Chip-Hong Chang, JiataoDing, RuiQiao, And Mathias Faust., 2017. Tap Delay-And-Accumulate Cost Aware Coefficient Synthesis Algorithm for the Design of Area-Power Efficient Fir Filters. IEEE Transactions on Circuits and Systems–I: Pp.1-11.

- Ahmed Liacha, Abdelkrim K. Oudjida, FaridFerguene, Mohammed Bakiri, Mohamed L. Berrandjia. Design Of High-Speed, Low-Power, And Areaefficientfir Filters. Iet Circuits Devices Syst., 2018, Vol. 12 Issue. 1, Pp. 1-11.

- 15. Ramanathan, S., GortyAnand, Prasanth Reddy, and Sri AdibhatlaSridevi. "Low Power Adaptive Fir FILTERS Based on Distributed Arithmetic." Int. Journal of Engineering Research and Applications 6, No. 5 (2016): 47-51.

- Dr. Seetaiah Kilaru, Hari Kishore K, Sravani T, Anvesh Chowdary L, Balaji T "Review and Analysis of Promising Technologies with Respect to fifth Generation Networks", 2014 First International Conference on Networks & Soft Computing, ISSN:978-1-4799-3486-7/14, pp.270-273, August 2014.

- A Murali, K Hari Kishore, C P Rama Krishna, S Kumar, A Trinadha Rao "Integrating the Reconfigurable Devices using Slow-changing Key Technique to achieve High Performance "Proceedings- 7th IEEE International Advance Computing Conference, IACC 2017, 7976849 ISSN: 2473-3571, pp.530-534, July 2017.

- Avinash Yadlapati, Kakarla Hari Kishore, "Constrained Level Validation of Serial Peripheral Interface Protocol", Proceedings of the First International Conference on SCI 2016, Volume 1, Smart Innovation, Systems and Technologies 77(Publisher: Springer Nature Singapore Pvt. Ltd), ISSN No: 2190-3018, ISBN: 978-981-10-5544-7, Chapter No: 77, pp. 743-753, 25th December 2017.

- Mahesh Madavath, Hari Kishore Kakarla, Azham Hussain, C.S. Boopathi"Design and Analysis of CMOS RF Receiver Front-End of LNA for Wireless Applications" Microprocessors and Microsystems, ISSN: 0141-9331, Volume-75, Article: 102999, June 2020

- 20. Avinash Yadlapati, Hari Kishore Kakarla"Low-power design-for-test implementation on phase-locked loop design" Measurement and Control, ISSN: 0020-2940, Volume-52, Issue No: (7-8), Page No: 995-1001, June 2019.

- 21. Nan Jiang, Abdol Ghaffar Ebadi, Kakarla Hari Kishore, Qahtan.A.Yousif, Mohammad Salmani "Thermomechanical Reliability Assessment of Solder Joints in a Photo-voltaic Module Operated in a Hot Climate" *IEEE Transactions on Components, Packaging and Manufacturing Technology*, P-ISSN: 2156-3950, E-ISSN: 2156-3985, Vol No: 10, Issue No: 1, Page No: 160-167, January 2020.

- 22. M. Kavitha, Zaid Hamid Mahmoud, Kakarla Hari Kishore, A.M. Petrov, Aleksandr Lekomtsev, Pavel Iliushin, Angelina Olegovna Zekiy, Mohammad Salmani "Application of Steinberg Model for Vibration Lifetime Evaluation of Sn-Ag-Cu based Solder Joints in Power Semiconductor" *IEEE Transactions on Components, Packaging and Manufacturing Technology*, P-ISSN: 2156-3950, E-ISSN: 2156-3985, January 2021.

- A. Surendar, K. H. Kishore, M. Kavitha, A. Z. Ibatova, V. Samavatian "Effects of Thermo-Mechanical Fatigue and Low Cycle Fatigue Interaction on Performance of Solder Joints" IEEE Transactions on Device and Materials Reliability, P-ISSN: 1530-4388, E-ISSN: 1558-2574, Vol No: 18, Issue No: 4, Page No: 606-612, December-2018.

- 23. A Murali, K Hari Kishore, G AAnitha Priyadarshini "Improved design debugging architecture using low power serial communication protocols for signal processing applications" International Journal of Speech Technology (Springer), ISSN No: 1572-8110, January 2021.

- 24. Raja Kumari Chilukuri, Hari Kishore Kakarla, K Subba Rao "Estimation of Modulation Parameters of LPI Radar using Cyclostationary Design of Reconfigurable Low Power Pipelined ADC for Bio-Impedance Measurement" Sensing and Imaging, ISSN: 1557-2072, Volume-51, Issue-1, October 2020.

- 25. B Srikanth, M Siva Kumar, J V R Ravindra, K Hari Kishore"The enhancement of security measures in advanced encryption standard using double precision floating point multiplication model" Transactions on Emerging Telecommunications Technologies, ISSN: 2161-3915, Volume: 31, Issue: 0, June 2020.

- 26. K Hari Kishore, Fazal Noorbasha, Katta Sandeep, D. N. V. Bhupesh, SK. Khadar Imran, K. Sowmya "Linear convolution using UT Vedic multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 409-418, March 2018.

- 27. Nadhindla Baladastagiri, Kakarla Hari Kishore, Vinit Kumar Gunjan and Shaik Fahimuddin, "Design of a Low-Power Low-Kickback-Noise Latched Dynamic Comparator for Cardiac Implantable Medical Device Applications", Proceedings of Lecture Notes in Electrical Engineering 434, pp. 637-645, ISSN No: 1876-1100, E-ISSN: 1876-1119, January 2018.

- 28. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019.

- 29. K.Sarath Chandra, K Hari Kishore "Electrical Characteristics of Double Gate FINFET under Different Modes of Operation" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 172-175, April 2019.

- P.Ramakrishna, M. Nagarani, K Hari Kishore "A Low Power 8-Bit Current-Steering DAC Using CMOS Technology" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 137-140, April 2019.

- 31. K Hari Kishore, Fazal Noorbasha, Katta Sandeep, D. N. V. Bhupesh, SK. Khadar Imran, K. Sowmya "Linear convolution using UT Vedic multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 409-418, March 2018.

- 32. K Hari Kishore, B. K. V. Prasad, Y. Manoj Sai Teja, D. Akhila, K. Nikhil Sai, P. Sravan Kumar "Design and comparative analysis of inexact speculative adder and multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 413-426, March 2018.

- 33. Nadhindla Baladastagiri, Kakarla Hari Kishore, Vinit Kumar Gunjan and Shaik Fahimuddin, "Design of a Low-Power Low-Kickback-Noise Latched Dynamic Comparator for Cardiac Implantable Medical Device Applications", Proceedings of Lecture Notes in Electrical Engineering 434, pp. 637-645, ISSN No: 1876-1100, E-ISSN: 1876-1119, January 2018.

- P.Ramakrishna, M. Nagarani, K Hari Kishore "A Low Power 8-Bit Current-Steering DAC Using CMOS Technology" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 137-140, April 2019.

- 35. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019.

- 36. K.Sarath Chandra, K Hari Kishore "Electrical Characteristics of Double Gate FINFET under Different Modes of Operation" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 172-175, April 2019.

- Avinash Yadlapati, K Hari Kishore "Implementation of Asynchronous FIFO using Low Power DFT" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6S, Page No: 152-156, April 2019.

- Chella Santhosh, K. Hari Kishore, G. Pavani Lakshmi, G.Kushwanth, P. Rama Krishna Dharma Teja, R. S. Ernest Ravindran, Sree Vardhan Cheerala, M. Ravi Kumar "Detection of Heavy Metal Ions using Star-Shaped Microfluidic Channel" International Journal of Emerging Trends in Engineering Research, ISSN: 2347-3983, Volume-7 Issue-12, Page No: 768-771, December 2019.

- 39. Mahesh Madavath, K Hari Kishore"Design and Analysis of Receiver Front-End of CMOS Cascode Common Source Stage with Inductive Degeneration Low Noise Amplifier on 65 nm Technology Process" Journal of Nanoscience and Nanotechnology, ISSN: 1546-1955, Volume-16, Issue No: (5-6), Page No: 2628-2634, June 2019.

- P Ramakrishna, K Hari Kishore"Implementation of Low Power and Area Efficient 7-Bit Flash Analog to Digital Converter" Journal of Nanoscience and Nanotechnology, ISSN: 1546-1955, Volume-16, Issue No: (5-6), Page No: 2213-2217, June 2019.

- 41. Ch. Naga Babu, P. Naga Siva Sai, Ch.Priyanka, K Hari Kishore, M.Bindu Bhargavi, K.Karthik "Comparative Analysis of High Speed Carry Skip Adders" International Journal of Engineering and Technology (UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.24, Page No: 121-125, April 2018.

- 42. G Siri Vennela, K Hari Kishore, E Raghuveera "High Accurate and Power Efficient ECG-Based Processor for Predicting Ventricular Arrhythmia" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 10, Issue No: 2, Page No: 1180-1121, May 2018.

- 43. P. Gopi Krishna, K. Sreenivasa Ravi, K Hari Kishore, K KrishnaVeni, K. N. Siva Rao, R.D Prasad "Design and Development of Bi-Directional IoT gateway using ZigBee and Wi-Fi technologies with MQTT Protocol" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 125-129, March 2018.

- 44. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019

- 45. K Divya Madhuri, K Hari Kishore "Implementation of 4-bit Ripple Carry Adder by Adopting Sub threshold Adiabatic Logic for Ultralow-Power Application" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 12, Issue No: 6, Page No: 11-17, May 2020.

- 46. Bhogadi Anil Kumar, Chillapalli Haritha, Gumpena Veda Sri Leela, E Raghuveera, K Hari Kishore" A Parametric DFT Scheme for RAMs" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 12, Issue No: 2, Page No: 2298-2305, May 2020.