Research Article

# Design and Analysis of FS-TSPC-DET Flip-Flop for IoT Applications

K.V.K.V.L Pavan Kumar<sup>1</sup>, V S V Prabhakar<sup>2</sup>, K. Naresh<sup>3</sup>, N. Gopi Krishna<sup>4</sup>, R. Sri Hari<sup>5</sup>

<sup>1,2,3,4,5</sup>Department of ECE, KoneruLakshmaiah Education Foundation, Vaddesaram-522502 <sup>1</sup>pavan.cec@gmail.com, <sup>2</sup>prabhakarvsv@kluniversity.in

Article History: Received: 11 January 2021; Accepted: 27 February 2021; Published online: 5 April 2021

**Abstract:** The paper outlines the utmost importance of energy-efficient devices for IoT applications and recommends adual edge-triggeredTSPC flip-flop in fully-static mode at 45nm technology with low supply rail carried out in CMOS using MENTOR GRAPHICS tool. The proposed flip-flop proved to be energy efficient compared to traditional double and single edge-triggered flip-flops in terms of latency, power, the figure of merit and area for IoT applications. A comparison of two types of dual-edge triggered flip-flops are analyzed concerning the mentioned performance metrics and deduces the best flip-flop for IoT applications. Clock overlap issues are turning down in dual edge-triggered TSPC flip-flopcompared with a conventional dual edge-triggered flip-flop in full static modeand allow stringent operation at 1V supply rail thatdelivers1.14uW power, 0.60fJ figure of merit and 531.99ps latency at 45nm CMOS.

**Keywords:** Power, Latency, True Single-Phase Clock (TSPC), Dual edge-triggered Flip-flop (DET-FF), Figure of merit (FOM), Internet of Things (IoT).

#### 1. Introduction

In a recentscenario, the Internet of Things (IoT) is the most emerging area in the era of healthcare and smart environments. IoT constitutes the vital components like objects & sensors. IoT devices mostly use the battery as a power source for their desired operation. It requires devices with maximum battery life, high speed and portable. The battery life is improved with a low voltage operation called voltage scaling. The speed of these devices is increased by minimizing un-necessary delays [1], [2]. These devices become portable by scaling down the length of the transistors to an optimum size. Several methods are utilized for low voltage operation and are achieved by sub-threshold techniques.

IoT devices utilize memory elements for data processing applications in various fields. Memory elements may be either a latch or a flip-flop. Flip-flops are the most vital components for present circuit design to store 1-bit of data. Flip-flops are sensitive to edges of the clock to perform storage operations. Besides storage, flip-flops are also used to synchronize the data flow. Hence, the synchronization is done throughout the entire clock [3]. A huge number of flip-flops are used in a regular processor, frequently many thousands. flip-flops involve an enormous part of the general circuit, decreasing power utilization has an extraordinary impact on system-level energy efficiency [4]. Particularly for energy-compelled IoT applications. Reducing power utilization in IoT integrated circuit is significant for increasing battery life. But flip-flops which are switch by every clock cycle, consume a huge part of the dynamic power in an organized system. Therefore, many experimenting works have been performed to create flip-flops with lower power utilization and better energy proficiency.

The most recommended procedure for a flip-flop is utilizing either the rising or falling edge of the clock as atrigger source for the switching operation. This kind of flip-flop is known as a Single-Edge-Triggered flip-flop (SET-FF) [1], [5], The other form of flip-flops are Dual edge-triggered flip-flops (DET-FF) use the both rising & falling edge of the clock to perform the desired operation. Utilization of both clock edges accomplishes better energy proficiency because it latches the data for both the edges. Therefore, the throughput of DET-FFis maximum than SET-FF compared at the same clock frequency. Hence, the DET-FFis proposed as an alternative sequential circuit element for low power utilization compared to SET-FF [6], [7].

SET FF & DET FF are realized by using severaldynamicCMOS logic styles like C-CMOS, Domino, N-P MOS, Dual threshold CMOS, Multi threshold CMOS, LVCMOS, TSPC logic. Of these, True single-phase clock (TSPC) logic-based flip-flopsdiminish the leakage current generated at the dynamic nodes and utilize the wide operational frequency range in the CMOS process. TSPC also performs the flip-flop operation with low power, delay and high clock speed [8] [9]. TSPC logic uses a single-phase clock to implement the latches and these latches are non-inverting. In TSPC logic, the functionality is embedded into the latch which reduces delay overhead provided by the latches.

In this paper, DET-FF's are realized by using TSPC logic because of its advantages compared with remaining logic styles. DET-FF's are implemented with TSPC by using both AND-OR logic and TRANSMISSION GATES at the output side as a MUX to produce necessary output Q. It provides a comparative analysis of both the flip-flops in terms of reliable parameters like power, latency and figure of merit (FOM). It also deduces the best DET-FF that suits IoT applications.

Meantime, a simple and widely designed technique is used for maximizing the energy efficiency in the electronic system is voltage scaling. By diminishing supply rail voltage  $V_{DD}$ , a quadratic drop in dynamic energy utilization was observed. Hence, voltage scaling can be widely used for the less energy-constrained IoT applications.

### 2. Proposed Art

The proposed art entitles Full Static-True Single-PhaseClock-Dual Edge Triggered Flip-Flop (FS-TSPC-DET-FF) that acts as Data Flip-Flop (D-FF) is implemented with TSPC logic and developed in 45nm CMOS technology using AND-OR logic & Transmission gate MUXas the output drivers to provide full voltage swing at the output node Q. It also provides a compact size flip-flop for portable IoT applications [10], [11].

Data Flip-Flopsarecommonlydesigned by using latches in cascaded nature.Latches that are usually available are positive latch and negative latch cascaded together to form a flip-flop or a register. Fig 1. shows the positive and negative latches cascaded together to form a D-flip-flop with D as its input, Q as the output. The operation of the D-FF signifies that the output is identical to the input. D-FF proposed in this era uses only a single-phase clock to carry out its operation [10], [12]. It presents the desired operation on both the edges of the clock (rising & falling edges). These latches are encapsulated with theoutput drivers like AND-OR gate, transmission gate MUXthatoperatesasDualEdge Triggered – Flip-Flop (DET-FF).

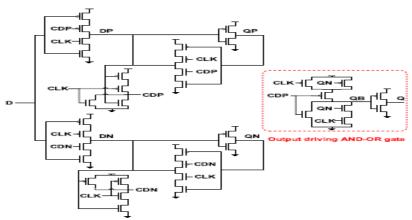

Figure 1.TSPC DET-FF with AND-OR Logic

The operations carried out in figures 1 & 2 are similar up to the output driver stage nodes QP & QN of the latches that are utilized in the D-FF. Figure 1 utilizes a clock (CLK) to accomplish the flip-flop operation. The proposed D-FF circuit uses two critical signals CDP, CDN across the positive & negative latches respectively to facilitate the desired operation. CDP, CDN are the two necessary signals generated from the NAND & NOR gates at the respective latches as in figures 1 & 2. In this era, CDP, CDN is used to provide strong pull-up/pull-down for the flip-flop. Likewise, it latches the outputs QP, QN to the output node Q. From Figures 1 & 2, the nodesDP, DN, QP, QN are the inputs & outputs of the latches respectively. The outputs that are latched on to the output node Q are dispute free logic values [10], [13], [14].

The Boolean expressions for CDP & CDN [10] are expressed by using CLK, DP, DN with the help of NOR, NAND gates for positive & negative latches respectively as indicated below IN equation (1) & (2).

The critical node values CDP, CDN depends on the QP, QN values generated from positive & negative latches respectively [10]. The output node Q is obtained with the help of CLK, QP & QN as stated below in equation (3).

$$Q = QN.CLK + QP.CLK'$$

(3)

As CLK='0' & D='0', the critical nodes are pre-charged to HIGH logic with CDP = CDN ='1', At the same time, the output node Q holds the previous state that is located at '0'. As the CLK only changes its transition from '0' to '1' and consider 'D' remains uniform that results in the changes of critical nodes CDP & CDN as CDP=CDN='0' and latches the output node Q ='0'.

As CLK='0' & D='1', the critical nodes are pre-charged with CDP = '0' & CDN ='1', At the same time, the output node Q produces '0'. As the CLK only changes its transition from '0' to '1' and consider 'D' remains uniform that results in the changes of critical nodes CDP & CDN as CDP='0' & CDN='1' and latches the output node Q='1'.

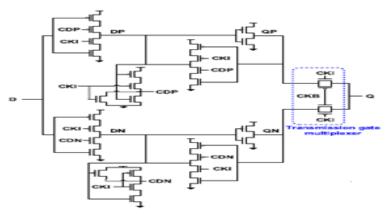

Figure 2. TSPC DET-FF with TG-MUX

The circuit proposed in figure 2 operates similarly to the circuit that is proposed in figure 1 up to the output driver stage. AND-ORoutput driver stage in figure 1 is replaced with transmission-gate based MUX to latch the QP, QN outputs to the output node Q. FS-TSPC DET-FF is proposed on MUX based topologyto allow CLK & CLKI to perform the D-FF operation. CLKI is the delayed CLK to overcome clock overlap issues during the operation. The use of CLKI in the figure 2 makes the circuit operate efficiently compared with figure 1. CLK & CLKI are primarily used to enable both the positive & negative latches at the same time to enhance the speed. A transmission gate-basedMUX, controlled by a two-phase clocklatch the data from both the latches to output node Q with minimized constraints [10], [15].

The transmission-gate MUX selects either QP or QN based on the selection line CLKB. As CLKB ='0', the output node Q=QP. and CLKB ='1', the output node Q=QN. CLKB is the inversion of the CLK to perform latching of the data from QP, QN to output node Q without disturbing the latch operation.

FS-TSPC DET-FF implemented with AND-OR logic circuit indicated in figure1 suffers from several conslikemore power and low speed of operation during the simulation. The cons specified across AND-OR logic is diminished by transmission-gate MUX. Figure2 also overcomes all clock overlap issues that were recognized in the existing circuits. Table 1. Shows the results of different CMOS technologies for the existing circuit [10], [16].

### 3. Results and Discussion

This section entitles the simulations carried out in the MENTOR GRAPHICS tool, cons that are observed in AND-OR logic, pros by using transmission-gate MUX, comparative analysis of both the circuits at circuit level in terms of several parameters, like, Power, Speed, Figure of Merit, etc. It recognizes the best-proposed latch to carry out desired IoT applications.

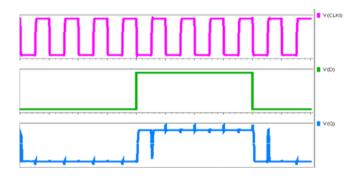

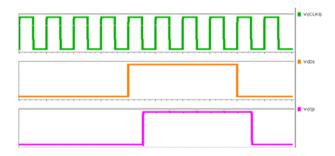

The simulation was carried out using the MENTOR GRAPHICS tool using 130nm, 90nm, 45nm CMOS process with  $V_{\rm DD}=1\rm V$  at 27°C temperature for both AND-OR logic transmission-gatebased MUX latches are mentioned in figures 1 & 2. ELDO Simulator is used to carry out simulations to reckon the parameters like power, latency and figure of merit for each technology parameter. Simulated waveforms of the AND-OR logic transmission-gate-based MUX latches are shown in figures 3 & 4 respectively [10], [17]. Figures 3 & 4 represent the simulated waveforms of AND-OR logic transmission-gate-based MUX latches that use CLK as the control signal to latch the input D to the output node Q. It is noticed that output Q of the AND-OR logic in figure suffers from glitches that increase the power dissipation of the latchand also degrade the output logic levels [10], [18], [19-51]. Figure4 presents the output waveform of the transmission-gate based MUX latch with glitch-free that diminishes the power dissipation and enhances the speed of operation to a great extent. The waveforms in figure 3 & 4 are simulated at a 45nm CMOS process.

Figure 3. Simulation waveform of AND-OR logic-based latch at 45nm CMOS

It is noticed from figures 3 & 5, the output logic at node Q is fully static with maximum voltage swings at logic '0' & logic '1' nodes respectively. It dictates that TSPC based circuits constitute logic'0' = 0V & logic '1' = VDD across the output nodes Q in both AND-OR, MUX based FS-TSPC DET-FF.

Figure 4. Simulation waveform of Transmission-gate based MUX latch at 45nm CMOS

The parametric values like power, latency & figure of merit of anFS-TSPC-DET FF implemented by using AND-OR logic-based MUX & transmission-gate-based MUX at different technology parameters are in Table 1. It is noticed that the Power, Latency & Figure of Merit is maximum at 130nm and minimum at 45nm CMOS process.

| Parameter            | AND OR DET-FF                           |        |        | TG DET-FF |        |        |

|----------------------|-----------------------------------------|--------|--------|-----------|--------|--------|

|                      | Supply Voltage = 1V, Temperature = 27°C |        |        |           |        |        |

| Technology           | 130                                     | 90     | 45     | 130       | 90     | 45     |

| Power (uW)           | 8.25                                    | 3.14   | 1.28   | 7.16      | 2.68   | 1.14   |

| Latency (ps)         | 620.20                                  | 560.44 | 544.19 | 573.50    | 540.80 | 531.59 |

| Figure of Merit (fJ) | 5.11                                    | 1.75   | 0.70   | 4.10      | 1.45   | 0.60   |

Table 1. Different Technology Parameters

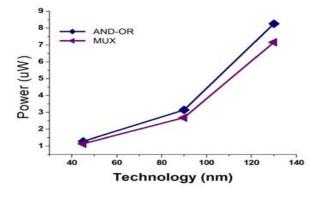

Figure 5. Graphical comparison of power with technology for FS-TSPC DET-FF

From Table 1 & Figure 5, Power dissipated from the latch is the average dynamic power dissipation evaluated from the waveforms using the ELDO simulator. The average dynamic power dissipation [3], [9] is evaluated theoretically by using equation (4) as

$$P_{\text{avg dynamic}} = C_L \cdot V_{DD}^2 \cdot f$$

(4)

From Equation (4),  $C_L$  dictates load capacitance of the latch at output node Q,  $V_{DD}$  dictates the supply voltage of the latch and f dictates the frequency of operation for the latch.

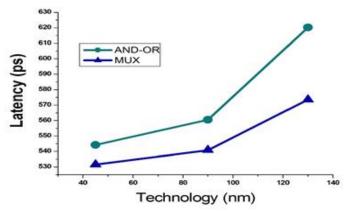

Figure 6. Graphical comparison of Latency with technology for FS-TSPC DET-FF

From Table1 & Figure6, Latency from the latch is the average delay evaluated from the waveforms between CLK & output node Q using the ELDO simulator. The latency exists only for sequential circuits that operate with the CLK.

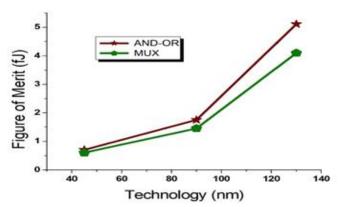

Figure 7. Graphical comparison of Figure of Merit with technology for FS-TSPC DET-FF

From Table 1 & Figure 7, the Figure of Merit from the latch is the average dynamic power dissipation multiplied with the Latency. Figure of Merit is evaluated theoretically by using equation (5) as

Figure of Merit (FOM) =

$$P_{\text{avg dynamic}}$$

\* Latency (5)

Figures 5,6,7 dictate the graphical comparison of power, latency & figure of merit with technology for AND-OR & MUX based FS-TSPC DET-FF varying from 130nm to 45nm CMOS process technology at a uniform temperature of  $27^{\circ}$ C, frequency = 1 GHz&  $V_{DD}$  = 1V. It is noticed that several parametric values like power, latency & figure of merit are maximum for AND-OR based FS-TSPC DET-FF compared with transmission-gate MUX based FS-TSPC DET-FF at 130nm, 90nm & 45nm respectively [10], [19]. It also dictates that as the technology scales down the parameters like power, latency & figure of merit also scale down respectively.

## 4. Conclusion

The conclusion dictates that transmission-gate MUXbased Fully static True single-phase Dual edge-triggered flip-flop (FS TSPC DET-FF) yields low power dissipation, high speed & optimized figure of merit at the output node Q compared with AND-OR based Fully static True single-phase Dual edge-triggered flip-flop

(FS TSPC DET-FF) at a uniform temperature of  $27^{\circ}$ C, frequency = 1 GHz &  $V_{DD}$  = 1V for 130nm, 90nm & 45nm technologies respectively. The transmission-gate MUXbased FS TSPC DET-FF yields optimized parametric values of Power = 1.14uW, Latency = 531.59ps & Figure of Merit = 0.60fJ at 45nm CMOS. It also dictates that transmission-gate MUX based FS TSPC DET-FF Power is diminished by 10%, Latency by 2% & Figure of merit by 14% at 45nm CMOS compared with AND-OR based FS TSPC DET-FF using MENTOR GRAPHICS tool and manifest that transmission-gate MUXbased FS TSPC DET-FF overcome clock overlap issues, furnishes voltage scaling down declares that it is best suitable for IoT applications.

### References

- 1. M. Afghahi and J. Yuan, "Double-edge-triggered D-flip-flops for high-speed CMOS circuits", IEEE J. Solid-State Circuits, vol. 26, no. 8, pp. 1168-1170, 1991.

- 2. P. Chandrakasan, S. Sheng and R. W. Brodersen, "Low-power CMOS digital design", IEEE J. Solid-State Circuits, vol. 27, no. 4, pp. 473-484, Apr. 1992.

- 3. Pavan Kumar, K. V., Sravanthi, G. L., Suresh Kumar, N., & Prabhakar, V. S. V. (2019). Performance analysis of 6transistor single bit adder element. International Journal of Innovative Technology and Exploring Engineering, 8(6), 1677-1681.

- 4. Gago, R. Escano and J. A. Hidalgo, "Reduced implementation of D-type DET flip-flops", IEEE J. Solid-State Circuits, vol. 28, no. 3, pp. 400-402, Mar. 1993.

- 5. R. P. Llopis and M. Sachdev, "Low power testable dual edge-triggered flip-flops", Proc. Int. Symp. Low Power Electron. Design (ISLPED), pp. 341-345, 1996.

- 6. Y.-Y. Sung and R. C. Chang, "A novel CMOS double-edge triggered flip-flop for low-power applications", Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), pp. 665, May 2004.

- 7. P. Zhao, J. McNeely, P. Golconda, M. A. Bayoumi, R. A. Barcenas and W. Kuang, "Low-power clock branch sharing double-edge triggered flip-flop", IEEE Trans. Very Large-Scale Integer. (VLSI) Syst., vol. 15, no. 3, pp. 338-345, Mar. 2007.

- 8. M. Alioto, E. Consoli and G. Palumbo, "DET FF topologies: A detailed investigation in the energy-delay-area domain", Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), pp. 563-566, May 2011.

- 9. Pavan Kumar, K. V. K. V. L., Sravanthi, G. L., Prabhakar, V. S. V., Vijaya Lakshmi, P., Bindu Priya, K., Sai Akhil, K., . . . Hari Kishore, K. (2019). Performance comparison of dynamic bias comparators. International Journal of Innovative Technology and Exploring Engineering, 8(7S), 110-114.

- 10. Y. Lee, G. Shin and Y. Lee, "A Fully Static True-Single-Phase-Clocked Dual-Edge-Triggered Flip-Flop for Near-Threshold Voltage Operation in IoT Applications," in IEEE Access, vol. 8, pp. 40232-40245, 2020, DOI: 10.1109/ACCESS.2020.2976773.

- 11. S. Muthu Kumar and G. Choi, "Low-power and area-efficient 9-transistor double-edge triggered flip-flop", IEICE Electron. Express, vol. 10, no. 18, 2013.

- Pavan Kumar, K. V. K. V. L., Ernest Ravindran, R. S., Prabhakar, V. S. V., Vardhan, T. H., Sathwik, P. J., & Kiran, N. H. (2020). Performance analysis of various full adders. International Journal of Advanced Science and Technology, 29(3), 591-598.

- 13. Y. Kim, "A static contention-free single-phase-clocked 24T flip-flop in 45 nm for low-power applications", IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 466-467, Feb. 2014.

- 14. Bonetti, A. Teman and A. Burg, "An overlap-contention free true-single-phase clock dual-edge-triggered flip-flop", Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), pp. 1850-1853, May 2015.

- 15. S. Paul, V. Honkote, R. Kim, T. Majumder, P. Aseron, V. Grossnickle, et al., "An energy harvesting wireless sensor node for IoT systems featuring a near-threshold voltage IA-32 microcontroller in 14nm tri-gate CMOS", Proc. IEEE Symp. VLSI Circuits (VLSI-Circuits), pp. 1-2, Jun. 2016.

- N. Lotze and Y. Manoli, "Ultra-sub-threshold operation of always-on digital circuits for IoT applications by use of Schmitt trigger gates", IEEE Trans. Circuits Syst. I Reg. Papers, vol. 64, no. 11, pp. 2920-2933, Nov. 2017.

- 17. F. Stas and D. Bol, "A 0.4-V 0.66-fJ/cycle retentive true-single-phase-clock 18T flip-flop in 28-nm fully-depleted SOI CMOS", IEEE Trans. Circuits Syst. I Reg. Papers, vol. 65, no. 3, pp. 935-945, Mar. 2018.

- 18. Pavan Kumar, K. V. K. V. L., Sravanthi, G. L., Lakshmana Kumar, M., Kumar, K. T. P. S., & Prabhakar, V. S. V. (2020). High-performance dynamic comparator. International Journal of Emerging Trends in Engineering Research, 8(9), 5545-5550. doi:10.30534/ijeter/2020/103892020

- 19. Y. Cai, A. Savanth, P. Prabhat, J. Myers, A. S. Weddell and T. J. Kazmierski, "Ultra-low power 18-transistor fully static contention-free single-phase clocked flip-flop in 65-nm CMOS", IEEE J. Solid-State Circuits, vol. 54, no. 2, pp. 550-559, Feb. 2019.

- 20. Dr. Seetaiah Kilaru, Hari Kishore K, Sravani T, Anvesh Chowdary L, Balaji T "Review and Analysis of Promising Technologies with Respect to fifth Generation Networks", 2014 First International Conference on Networks & Soft Computing, ISSN:978-1-4799-3486-7/14,pp.270-273,August2014.

- 21. A Murali, K Hari Kishore, C P Rama Krishna, S Kumar, A Trinadha Rao "Integrating the Reconfigurable Devices using Slow-changing Key Technique to achieve High Performance "Proceedings- 7th IEEE International Advance Computing Conference, IACC 2017, 7976849 ISSN: 2473-3571, pp.530-534, July 2017.

- 22. Avinash Yadlapati, Kakarla Hari Kishore, "Constrained Level Validation of Serial Peripheral Interface Protocol", Proceedings of the First International Conference on SCI 2016, Volume 1, Smart Innovation, Systems and Technologies 77 (Publisher: Springer Nature Singapore Pvt. Ltd), ISSN No: 2190-3018, ISBN: 978-981-10-5544-7, Chapter No: 77, pp. 743-753, 25th December 2017.

- Mahesh Madavath, Hari Kishore Kakarla, Azham Hussain, C.S. Boopathi "Design and Analysis of CMOS RF Receiver Front-End of LNA for Wireless Applications" Microprocessors and Microsystems, ISSN: 0141-9331, Volume-75, Article: 102999, June 2020

- 24. Avinash Yadlapati, Hari Kishore Kakarla "Low-power design-for-test implementation on phase-locked loop design" Measurement and Control, ISSN: 0020-2940, Volume-52, Issue No: (7-8), Page No: 995-1001, June 2019.

- 25. Nan Jiang, Abdol Ghaffar Ebadi, Kakarla Hari Kishore, Qahtan.A.Yousif, Mohammad Salmani "Thermomechanical Reliability Assessment of Solder Joints in a Photo-voltaic Module Operated in a Hot Climate" *IEEE Transactions on Components, Packaging and Manufacturing Technology*, P-ISSN: 2156-3950, E-ISSN: 2156-3985, Vol No: 10, Issue No: 1, Page No: 160-167, January 2020.

- 26. M. Kavitha, Zaid Hamid Mahmoud, Kakarla Hari Kishore, A.M. Petrov, Aleksandr Lekomtsev, Pavel Iliushin, Angelina Olegovna Zekiy, Mohammad Salmani "Application of Steinberg Model for Vibration Lifetime Evaluation of Sn-Ag-Cu based Solder Joints in Power Semiconductor" *IEEE Transactions on Components, Packaging and Manufacturing Technology*, P-ISSN: 2156-3950, E-ISSN: 2156-3985, January 2021.

- 27. Surendar, K. H. Kishore, M. Kavitha, A. Z. Ibatova, V. Samavatian "Effects of Thermo-Mechanical Fatigue and Low Cycle Fatigue Interaction on Performance of Solder Joints" IEEE Transactions on Device and Materials Reliability, P-ISSN: 1530-4388, E-ISSN: 1558-2574, Vol No: 18, Issue No: 4, Page No: 606-612, December-2018.

- 28. A Murali, K Hari Kishore, G A Anitha Priyadarshini "Improved design debugging architecture using low power serial communication protocols for signal processing applications" International Journal of Speech Technology (Springer), ISSN No: 1572-8110, January 2021.

- 29. Raja Kumari Chilukuri, Hari Kishore Kakarla, K Subba Rao "Estimation of Modulation Parameters of LPI Radar using Cyclostationary Design of Reconfigurable Low Power Pipelined ADC for Bio-Impedance Measurement" Sensing and Imaging, ISSN: 1557-2072, Volume-51, Issue-1, October 2020.

- 30. B Srikanth, M Siva Kumar, J V R Ravindra, K Hari Kishore "The enhancement of security measures in advanced encryption standard using double precision floating point multiplication model" Transactions on Emerging Telecommunications Technologies, ISSN: 2161-3915, Volume: 31, Issue: 0, June 2020.

- 31. K Hari Kishore, Fazal Noorbasha, Katta Sandeep, D. N. V. Bhupesh, SK. Khadar Imran, K. Sowmya "Linear convolution using UT Vedic multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 409-418, March 2018.

- 32. Nadhindla Bala Dastagiri, Kakarla Hari Kishore, Vinit Kumar Gunjan and Shaik Fahimuddin, "Design of a Low-Power Low-Kickback-Noise Latched Dynamic Comparator for Cardiac Implantable Medical Device Applications", Proceedings of Lecture Notes in Electrical Engineering 434, pp. 637-645, ISSN No: 1876-1100, E-ISSN: 1876-1119, January 2018.

- 33. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019.

- 34. K.Sarath Chandra, K Hari Kishore "Electrical Characteristics of Double Gate FINFET under Different Modes of Operation" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 172-175, April 2019.

- 35. P.Ramakrishna, M. Nagarani, K Hari Kishore "A Low Power 8-Bit Current-Steering DAC Using CMOS Technology" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 137-140, April 2019.

- 36. K Hari Kishore, Fazal Noorbasha, Katta Sandeep, D. N. V. Bhupesh, SK. Khadar Imran, K. Sowmya "Linear convolution using UT Vedic multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 409-418, March 2018.

- 37. K Hari Kishore, B. K. V. Prasad, Y. Manoj Sai Teja, D. Akhila, K. Nikhil Sai, P. Sravan Kumar "Design and comparative analysis of inexact speculative adder and multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 413-426, March 2018.

- 38. Nadhindla Bala Dastagiri, Kakarla Hari Kishore, Vinit Kumar Gunjan and Shaik Fahimuddin, "Design of a Low-Power Low-Kickback-Noise Latched Dynamic Comparator for Cardiac Implantable Medical Device Applications", Proceedings of Lecture Notes in Electrical Engineering 434, pp. 637-645, ISSN No: 1876-1100, E-ISSN: 1876-1119, January 2018.

- 39. P.Ramakrishna, M. Nagarani, K Hari Kishore "A Low Power 8-Bit Current-Steering DAC Using CMOS Technology" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 137-140, April 2019.

- 40. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019.

- 41. K.Sarath Chandra, K Hari Kishore "Electrical Characteristics of Double Gate FINFET under Different Modes of Operation" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 172-175, April 2019.

- 42. Avinash Yadlapati, K Hari Kishore "Implementation of Asynchronous FIFO using Low Power DFT" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6S, Page No: 152-156, April 2019.

- 43. Chella Santhosh, K. Hari Kishore, G. Pavani Lakshmi, G.Kushwanth, P. Rama Krishna Dharma Teja, R. S. Ernest Ravindran, Sree Vardhan Cheerala, M. Ravi Kumar "Detection of Heavy Metal Ions using Star-Shaped Microfluidic Channel" International Journal of Emerging Trends in Engineering Research, ISSN: 2347-3983, Volume-7 Issue-12, Page No: 768-771, December 2019.

- 44. Mahesh Madavath, K Hari Kishore "Design and Analysis of Receiver Front-End of CMOS Cascode Common Source Stage with Inductive Degeneration Low Noise Amplifier on 65 nm Technology Process" Journal of Nanoscience and Nanotechnology, ISSN: 1546-1955, Volume-16, Issue No: (5-6), Page No: 2628-2634, June 2019.

- 45. P Ramakrishna, K Hari Kishore "Implementation of Low Power and Area Efficient 7-Bit Flash Analog to Digital Converter" Journal of Nanoscience and Nanotechnology, ISSN: 1546-1955, Volume-16, Issue No: (5-6), Page No: 2213-2217, June 2019.

- 46. Ch. Naga Babu, P. Naga Siva Sai, Ch.Priyanka, K Hari Kishore, M.Bindu Bhargavi, K.Karthik "Comparative Analysis of High Speed Carry Skip Adders" International Journal of Engineering and Technology (UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.24, Page No: 121-125, April 2018.

- 47. G Siri Vennela, K Hari Kishore, E Raghuveera "High Accurate and Power Efficient ECG-Based Processor for Predicting Ventricular Arrhythmia" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 10, Issue No: 2, Page No: 1180-1121, May 2018.

- 48. P. Gopi Krishna, K. Sreenivasa Ravi, K Hari Kishore, K KrishnaVeni, K. N. Siva Rao, R.D Prasad "Design and Development of Bi-Directional IoT gateway using ZigBee and Wi-Fi technologies with MQTT Protocol" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 125-129, March 2018.

- 49. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019.

- 50. K Divya Madhuri, K Hari Kishore "Implementation of 4-bit Ripple Carry Adder by Adopting Sub threshold Adiabatic Logic for Ultralow-Power Application" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 12, Issue No: 6, Page No: 11-17, May 2020.

- 51. Bhogadi Anil Kumar, Chillapalli Haritha, Gumpena Veda Sri Leela, E Raghuveera, K Hari Kishore" A Parametric DFT Scheme for RAMs" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 12, Issue No: 2, Page No: 2298-2305, May 2020.