# Design of 16-Bit SAR ADC Using DTMOS Technique

## Yarlagadda Archana<sup>1\*</sup>, Kakarla Hari Kishore<sup>2</sup>

<sup>1,2</sup>Department of ECE, Koneru Lakshmaiah Education Foundation, Vaddeswaram, Guntur, Andhra Pradesh, India

<sup>1\*</sup>archana.yarlagadda4@gmail.com,<sup>2</sup>kakarla.harikishore@gmail.com

Article History: Received: 11 January 2021; Accepted: 27 February 2021; Published online: 5 April 2021

**Abstract:** This paper presents a 16-bit 100MS/s SAR ADC with 1V power supply for biomedical implant systems developed with low power technique i.e., DTMOS logic. It consists of a R-2R DAC, low-power comparator, a digital SAR logic with low-leakage. The designed comparator is a differential architecture that has used to have an excellent, common-mode noise rejection. Comparator was created for proper operation to remain in saturation and could be used with differential amplifier. The comparator is the chief block of power consumption, so we focused mainly much of ability we make to design this module. The ADC is designed using Cadence virtuoso with CMOS 45nm technology. For SFDR, SNR, ENOB and power consumption, the converter utilizes 63.97dB, 51.06 dB, 15.15 and 528.8uw.

Keywords: Comparator, Control logic, DAC, Low Power, SAR ADC

## 1. Introduction

The role of ADC is vital in the bi-signal processing; for noiseless signal processing, data conversion is essential. In the proposed physiological transmission system, the captured signals from the human body after amplification and feature extraction are then converted into digital form by ADC and processed to the receiver [58]. Data converters are essential in the signal acquisition board; they are the bridge between analog and digital form. For physiological signals, data converters speed is not much concern. These devices are implanted on the human body since they should be operated with ultra-low power and powered by harvested energy [59-60]. So by combining these two features with the required accuracy and resolution completes the design of ADC. In this thesis, it is highly concentrated on low power consumption with minimized supply voltages with low power optimized techniques. If the main criteria are higher resolution, then the ADC Sigma Delta (or ADC form implementation) is introduced. It's the most sluggish ADC and it's complex settingtoo. Several improved and hybrid systems includingsuch as Flash pipeline, SAR pipeline, SARflash is developed and discussed [1].to enhance processing speed and power consumption optimization. These ADCs have reduced the group of components, and that is not better to adjust power consumption beyond a certain limit.SAR ADC has becoming a bigger subject to study for its excellent power efficiency. It will be used for applications of medium resolution, high speed and low power and small section. This is in the making of an appropriate option such as biomedical purposes.Software too. It consumes less power to its simple structure and therefore innovation scalable as all with its elements or parts are digital other than a comparator. There were some other tasks connected to improve SAR ADC results and this document focus mostly for the extraction of loads. The differential amplifier was used even with fewer disturbances and higher standard noise reduction mode and common source amplifier phase have been used as a second amplification phase and level to keep the transistor in the area of saturation Section II defines the mainSAR ADC architecture. Section III describes various structures of the architecture as well as its diagrams and operation of the control logic. The observations and analysis of the simulation are given in the Section IV and Section V accordingly.

## 2. SAR ADC Structure

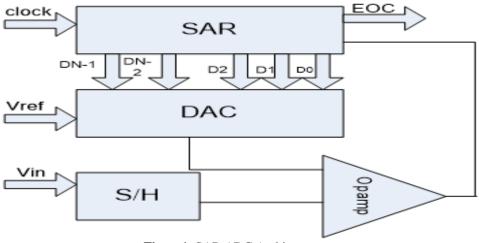

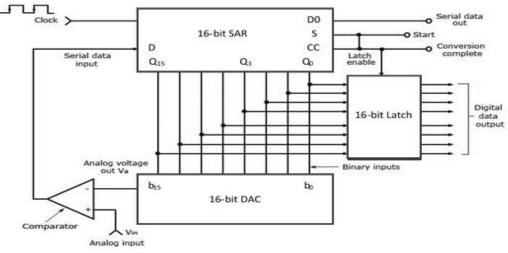

SAR ADC structured of a sample and hold circuit(S / H) that samples the analog input signal; comparator cont rasts the performance of DAC to the on being sampled (reference) signal; a DAC that gets the value analog of control logic result (SAR); and checking SAR logic which decides every bit [2]. The SAR ADC design can be seen in the figure 1.

Figure1. SAR ADC Architecture

#### 3. Design of SAR ADC

#### A. Track and Hold Circuit

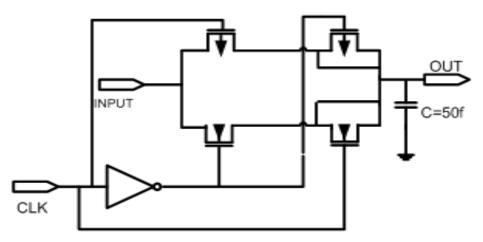

An equivalent Sample and hold circuit is a device in which specified span is used to obtain voltage constantly variable analog signals and locks at a stable value. These are fundamental analog memory instruments that are applied in ADC to get out of some input signal gap which will occur harm mechanism of change. Using a condenser, this sample and hold circuit keeps electrical charge to it and then maintains. At only one switching system such as transistor in the field effect and one active amplifier sample and hold samples the input data and gives to comparator.

Figure 2. Track and hold circuit

The op amp will switch off and high impedance will be maintained for its output. Unit gain buffer linked take the sample and keep the output phase will be always functional during both sample and hold mode and gives the voltage on hold condenser using the sampling and retaining circuit. Using anoperational amplifier, it displays the track and hold circuit. It being connected by the transition to two op-amps. The sampling method will be on when the switch is in lock state. If the switch is unlocked, the holding will be activated. Connecting the condenser to the second op-amp implies keeping the condenser. We obtain samples of analog signals with the help of the condenser by using the sample and hold circuit. For a certainperiod of time, it maintains samples. When a stable signal is generated, the analog to digital converter can be used to alter it into a digital signal.

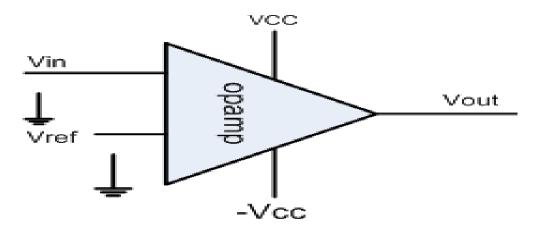

#### **B.** Comparator

A comparator is an electronic device that contrasts with two input values are added to it, generating. The comparator's performance value specifies which input is higher otherwise lower. Realize this comparator falls within the range of applications of non-linear IC that comparator is the primary power consumptionblock in the structure that's the thing much of the progress has been put over this section. The comparator produces a high or

low logic output factor depends between analog input and band gap voltage. For this function the comparator becomes an improved operational speed andstrong resolution.

Figure 3.Op amp as comparator

## C. Digital to Analog Converter

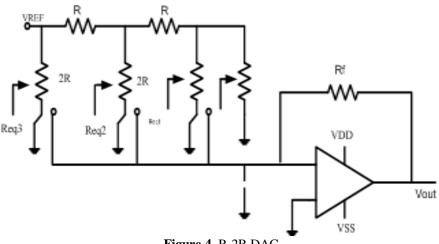

The R-2R DAC is a modification to the DAC model of the binary weighted resistor ladder where only two resistor values are used. The resistor ladder in R-2R DAC is designed to connect resistors in series with resistor value R, then 2R resistor rungs can be represented as in current mode or voltage mode depending on the reference voltage. Switches operated in voltage mode between Vref and ground and the switches operate in current mode of R-2R DAC is that it needs only resistors with only two values of resistance and 2N is the number of resistors. The output impedance for this model is always constant due to the 2R resistance of the ladder rung on each side. Current source transistors are used to increase the linearity of this system in combination with the resistor ladder network. To change the reference voltage between ground and digital level, a physical amplifier must be used. This limits the bandwidth and linearity errors can occur with the use of the op amp output buffer.

Figure 4. R-2R DAC

Switches operate between ground and Vref in voltage mode, which is difficult to design. Since the switches are directly connected to the output node, there will be glitches in the current mode.

#### D. Successive Approximation Register Logic

Successive Approximation Register (SAR) control logic determines each bit successively. Basically the Successive Approximation (SA) register contains N flip flops for an N-bit ADC and some combinational logic. It implements its operation with the binary search algorithm. SAR ADC performs all possible bits of binary search. Each bit has three options: it can be set to '1,' it can be set to '0 or maintains its value. The operation is briefly explained as:

The SAR is reset at the start of the conversion cycle by holding a high start signal. MSB bit is set to '1' on th e positive edge of the first clock pulse and reset other bits ('0'). This digital word is then created by the DAC ana log equivalent. The comparator compares the DAC output to the analog input signal being sampled. The compar ator gives LOW output if the DAC output is lower than the sampled input. and the SAR MSB will be reset ('0'). If the DAC output is lower than the sampled input, the comparator gives HIGH output and the SAR MSB will be held and on the positive edge of the next clock pulse the next MSB will be set ('). For the other bits, the same pro cess is repeated until each SAR bit is determined. Once LSB is tried, the SAR forces the full HIGH conversion si gnal to enable the latch to digitally deliver the valid data. In this case, for "N" bit ADC, "N+1" clock cycles are r equired.

The SAR conversion uses a binary search algorithm as its name implies. The inner circuit is therefore much easier to run than the full ADC sampling frequency. In general, the inner circuit runs at least as quickly like resolution for the Analog-to-Digital Convertersample rate. Thus a 10 bit, 1 MS/S SAR ADC [4].internally does not operate any slower than 10 MHz, allowing for the resolution of all 10 bits in one sample time. An SAR ADC's fundamental structure is very basic and can be seen in Figure even though it developed over the years with further variations and development.

Figure 5. Schematic View of SAR ADC

## 4. DTMOS Logic

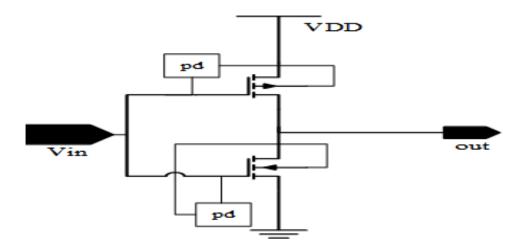

#### Figure 6. DTMOS inverter

For adaptivethreshold CMOS, their pinch off voltage was changed progressively match its operational status upon the device here the NMOS and PMOS transistor body is biased dynamically. Sufficient body biasing voltage to both PMOS and NMOS transistors are provided by the potential dividers which are connected to the input for that inverter. The maximum input impedance in ideal mode provides lower conduction losses whereas a small voltage level makes to large output switches in aggressive state. It could attain adaptive CMOS threshold

while binding the gate with body attached. DTMOS input power is constrained mostly by constructed-in diode ability in mass silicon machineries. A p-n diode must be negative voltage among source and body.

#### 5. Results and Exploration

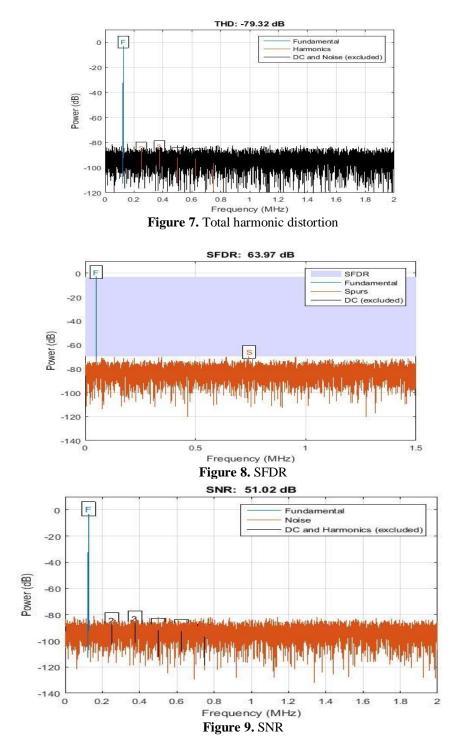

Figure 7 shows the calculated *SNR of* 51.02 dB for 16bit. The blue color line denoted with 'F' is indicates fundamental power, orange lines indicate the noise. The figure 8 shows square boxes with numbers are indicates the harmonics presented.

Figure 9 shows the calculated the Spurious Free Dynamic Range (*SFDR*) of 63.97 dB for 12bit. The portion shade with blue color is SFDR and 'F' is indicates fundamental power, S is the spurs.

Hence results obtained during this aspect can be found in this chapter, where their implications are addressed as well as the use of CMOS 45 nm technology for circuit implementation.

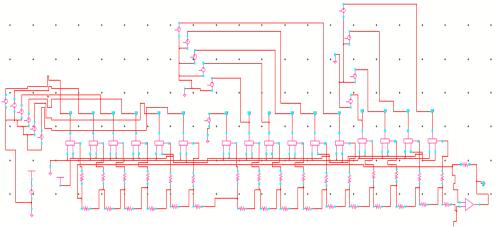

Figure 10.Schematic of R-2R DAC

|                     | This work   | [7]     | [8]   | [6]    | [9]         |

|---------------------|-------------|---------|-------|--------|-------------|

| Architecture        | SAR         | SAR     | SAR   | SAR    | SAR         |

| VDD[V]              | 1           | 1       | 1     | 1      | 1.2         |

| Power               | 528.8 μW    | 127.8µW | 820µW | 0.98mW | 0.826mW     |

| Technology(nm)      | 45          | 180     | 65    | 90     | 130         |

| Resolution (bits)   | 16          | 10      | 10    | 10     | 10          |

| F <sub>sample</sub> | 100Msps     | -       | -     | 30Msps | 50Msps      |

| DNL(LSB)            | +0.66/-0.52 | -       | -     | -      | +0.91/-0.63 |

| INL(LSB)            | +0.4/-0.33  | -       | -     | -      | +1.27/-1.36 |

| SFDR (dB)           | 63.97       | -       | 75.2  | -      | 65.9        |

| SNR (dB)            | 51.02       | -       | 56.9  | 57     | 57          |

| ENOB                | 15.15       | -       | 9.16  | 9.16   | 9.18        |

**Table 1.**Comparison with existing one

## 6. Conclusion

This paper16-bitsuccessive ADC approximation is functionally concluded with 1V supply voltage and which is simulated in cadence 45nm CMOS technology this paper mainly focusses on. Minimum power comparator and Digital-to-analog converter(DAC) as more power is used by SAR ADC. The SAR ADC is more appropriate to biomedical applications.

## References

- A. Achill, and Sunil Jacob, "Design of 9-bit SAR ADC using high speed and high resolution open loop CMOS comparator in 180nm technology with R-2R DAC topology," International Journal of VLSI and Embedded Systems-IJVES, vol 05, article. 11492, pp. 1391-1396. November 2014.

- 7. Jhin Fang Huang, Jin Yu Wen, and Cheng Ku Hsieh, "An 8 bit 20 MS/s successive approximation register analog to digital converter with low input capacitance," International Journal of Engineering Practical Research, vol. 3, issue. 4, pp. 83-88, November 2014.

- 8. Yu Meng, Wu Lipeng, Li Fule, and Wang Zhihua, "An 8 bit 12 MS/s asynchronous successive approximation register ADC with an on-chip reference," Journal of Semiconductors, vol. 34, no. 2, pp. 25010(1)25010(5), February 2013.

- 9. Yulin Zhang, GuiliangGuo, Yuepeng Yan, and Tao Yang, "Asynchronous 10MS/s 10-Bit SAR ADC for wireless network," International Journal of Computer Theory and Engineering, vol. 6, no. 6, pp. 443-446, December 2014.

- Yan Zhu, C. H. Chan, U. F. Chio, S. W. Sin, Seng-Pan U, R. P. Martins, and F. Maloberti, "Split-SAR ADCs: improved linearity with power and speed optimization," IEEE Transaction on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 2, pp.372-383, February 2014.

- G. Huang, S. Chang, C. Liu, and Y. Lin, "10-bit 30-MS/s SAR ADC Using a Switchback Switching Method," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, no. 3, pp. 584-588, March 2013.

- L. Xie, W. Nie, L. Xiong, and J. Su, "Energy-efficient capacitor-swapping reset scheme with MSB-split DAC for SAR ADCs," in Electronics Letters, vol. 53, no. 7, pp. 458-459, 30 3 2017, doi: 10.1049/el.2017.0422.

- 13. Van Rethy J, De Smedt M, Verhelst M, Gielen G (2013) Predictive sensing in analog-to-digital converters for biomedical applications. In: International symposium on signals, circuits and systems ISSCS2013, Iasi, pp 1–4.

- B. Lu and D. Huang, "A 10-Bits 50-MS/s SAR ADC Based on Area-Efficient and Low-Energy Switching Scheme," in *IEEE Access*, vol. 8, pp. 28257-28266, 2020.

- Md. Kareemoddin, A. Ashok Kumar, and Dr. Syed Musthak Ahmed, "Design of low power comparator for SAR ADC in biomedical applications," International Journal of Innovative Research in Computer and Communication Engineering, vol. 1, issue. 5, pp. 1161-1167, July 2013.

- 15. Brian P. Ginsburg, and Anantha P. Chandrakasan, "An energy-efficient charge recycling approach for a SAR converter with capacitive DAC," pp. 184-187, IEEE 2005.

- 16. K. Lokesh Krishna, and T. Ramashri, "VLSI design of 12 bit ADC with 1GSPS in 180nm CMOS integrating with SAR and two- step flash ADC," Journal of Theoretical and Applied Information Technology, vol. 68, no. 1, pp. 27-35, October 2014.

- J. A. Pieter Harpe, Cui Zhou, Yu Bi, P. Nick Vander Meijs, Xiaoyan Wang, Kathleen Philips, Guido Dolmans, and Harmke de Groot, "A 26 W 8 bit 10 MS/s asynchronous SAR ADC for low energy radios,"IEEE Journal of Solid State Circuits, vol. 46, no. 7, pp. 1585-1595, JULY 2011.

- Ryota Sekimoto, Akira Shikata, Kentaro Yoshioka, Tadahiro Kuroda, and Hiroki Ishikuro, "A 0.5-V 5.2-fJ/conversion-step full asynchronous SAR ADC with leakage power reduction down to 650 pW by boosted self-power gating in 40-nm CMOS," IEEE Journal of Solid State Circuits, vol. 48, no. 11, pp. 2628-2636, November 2013.

- 19. Wang Ya, Xue Chunying, Li Fule, Zhang Chun, and Wang Zhihua, "A low power 11-bit 100 MS/s SAR ADC," Journal of Semiconductors, vol. 36, no. 2, pp. 025003(1)-025003(5), February 2015.

- HarshitDosi, and RekhaAgrawal, "Low Power 8-bit Analog to Digital Converter (ADC) in 180 nm CMOS Technology," International Journal of Science and Research, vol. 2, issue. 7, pp. 417-418, July 2013.

- Dr. Seetaiah Kilaru, Hari Kishore K, Sravani T, Anvesh Chowdary L, Balaji T "Review and Analysis of Promising Technologies with Respect to fifth Generation Networks", 2014 First International Conference on Networks & Soft Computing, ISSN:978-1-4799-3486-7/14,pp.270-273,August2014.

- 22. A Murali, K Hari Kishore, C P Rama Krishna, S Kumar, A Trinadha Rao "Integrating the Reconfigurable Devices using Slow-changing Key Technique to achieve High Performance "Proceedings- 7th IEEE International Advance Computing Conference, IACC 2017, 7976849 ISSN: 2473-3571, pp.530-534, July 2017.

- Avinash Yadlapati, Kakarla Hari Kishore, "Constrained Level Validation of Serial Peripheral Interface Protocol", Proceedings of the First International Conference on SCI 2016, Volume 1, Smart Innovation, Systems and Technologies 77 (Publisher: Springer Nature Singapore Pvt. Ltd), ISSN No: 2190-3018, ISBN: 978-981-10-5544-7, Chapter No: 77, pp. 743-753, 25th December 2017.

- Mahesh Madavath, Hari Kishore Kakarla, Azham Hussain, C.S. Boopathi "Design and Analysis of CMOS RF Receiver Front-End of LNA for Wireless Applications" Microprocessors and Microsystems, ISSN: 0141-9331, Volume-75, Article: 102999, June 2020

- 25. Avinash Yadlapati, Hari Kishore Kakarla "Low-power design-for-test implementation on phase-locked loop design" Measurement and Control, ISSN: 0020-2940, Volume-52, Issue No: (7-8), Page No: 995-1001, June 2019.

- 26. Nan Jiang, Abdol Ghaffar Ebadi, Kakarla Hari Kishore, Qahtan.A.Yousif, Mohammad Salmani "Thermomechanical Reliability Assessment of Solder Joints in a Photo-voltaic Module Operated in a Hot Climate" IEEE Transactions on Components, Packaging and Manufacturing Technology, P-ISSN: 2156-3950, E-ISSN: 2156-3985, Vol No: 10, Issue No: 1, Page No: 160-167, January 2020.

- 27. M. Kavitha, Zaid Hamid Mahmoud, Kakarla Hari Kishore, A.M. Petrov, Aleksandr Lekomtsev, Pavel Iliushin, Angelina Olegovna Zekiy, Mohammad Salmani "Application of Steinberg Model for Vibration Lifetime Evaluation of Sn-Ag-Cu based Solder Joints in Power Semiconductor" IEEE Transactions on Components, Packaging and Manufacturing Technology, P-ISSN: 2156-3950, E-ISSN: 2156-3985, January 2021.

- A. Surendar, K. H. Kishore, M. Kavitha, A. Z. Ibatova, V. Samavatian "Effects of Thermo-Mechanical Fatigue and Low Cycle Fatigue Interaction on Performance of Solder Joints" IEEE Transactions on Device and Materials Reliability, P-ISSN: 1530-4388, E-ISSN: 1558-2574, Vol No: 18, Issue No: 4, Page No: 606-612, December-2018.

- 28. A Murali, K Hari Kishore, G A Anitha Priyadarshini "Improved design debugging architecture using low power serial communication protocols for signal processing applications" International Journal of Speech Technology (Springer), ISSN No: 1572-8110, January 2021.

- Raja Kumari Chilukuri, Hari Kishore Kakarla, K Subba Rao "Estimation of Modulation Parameters of LPI Radar using Cyclostationary Design of Reconfigurable Low Power Pipelined ADC for Bio-Impedance Measurement" Sensing and Imaging, ISSN: 1557-2072, Volume-51, Issue-1, October 2020.

- B Srikanth, M Siva Kumar, J V R Ravindra, K Hari Kishore "The enhancement of security measures in advanced encryption standard using double precision floating point multiplication model" Transactions on Emerging Telecommunications Technologies, ISSN: 2161-3915, Volume: 31, Issue: 0, June 2020.

- 31. K Hari Kishore, Fazal Noorbasha, Katta Sandeep, D. N. V. Bhupesh, SK. Khadar Imran, K. Sowmya "Linear convolution using UT Vedic multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 409-418, March 2018.

- 32. Nadhindla Bala Dastagiri, Kakarla Hari Kishore, Vinit Kumar Gunjan and Shaik Fahimuddin, "Design of a Low-Power Low-Kickback-Noise Latched Dynamic Comparator for Cardiac Implantable Medical Device Applications", Proceedings of Lecture Notes in Electrical Engineering 434, pp. 637-645, ISSN No: 1876-1100, E-ISSN: 1876-1119, January 2018.

- 33. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019.

- K. Sarath Chandra, K Hari Kishore "Electrical Characteristics of Double Gate FINFET under Different Modes of Operation" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 172-175, April 2019.

- P.Ramakrishna, M. Nagarani, K Hari Kishore "A Low Power 8-Bit Current-Steering DAC Using CMOS Technology" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 137-140, April 2019.

- 36. K Hari Kishore, Fazal Noorbasha, Katta Sandeep, D. N. V. Bhupesh, SK. Khadar Imran, K. Sowmya "Linear convolution using UT Vedic multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 409-418, March 2018.

- 37. K Hari Kishore, B. K. V. Prasad, Y. Manoj Sai Teja, D. Akhila, K. Nikhil Sai, P. Sravan Kumar "Design and comparative analysis of inexact speculative adder and multiplier" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 413-426, March 2018.

- Nadhindla Bala Dastagiri, Kakarla Hari Kishore, Vinit Kumar Gunjan and Shaik Fahimuddin, "Design of a Low-Power Low-Kickback-Noise Latched Dynamic Comparator for Cardiac Implantable Medical Device Applications", Proceedings of Lecture Notes in Electrical Engineering 434, pp. 637-645, ISSN No: 1876-1100, E-ISSN: 1876-1119, January 2018.

- P.Ramakrishna, M. Nagarani, K Hari Kishore "A Low Power 8-Bit Current-Steering DAC Using CMOS Technology" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 137-140, April 2019.

- 40. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019.

- K.Sarath Chandra, K Hari Kishore "Electrical Characteristics of Double Gate FINFET under Different Modes of Operation" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 172-175, April 2019.

- 42. Avinash Yadlapati, K Hari Kishore "Implementation of Asynchronous FIFO using Low Power DFT" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6S, Page No: 152-156, April 2019.

- 43. Chella Santhosh, K. Hari Kishore, G. Pavani Lakshmi, G.Kushwanth, P. Rama Krishna Dharma Teja, R. S. Ernest Ravindran, Sree Vardhan Cheerala, M. Ravi Kumar "Detection of Heavy Metal Ions using Star-Shaped Microfluidic Channel" International Journal of Emerging Trends in Engineering Research, ISSN: 2347-3983, Volume-7 Issue-12, Page No: 768-771, December 2019.

- 44. Mahesh Madavath, K Hari Kishore "Design and Analysis of Receiver Front-End of CMOS Cascode Common Source Stage with Inductive Degeneration Low Noise Amplifier on 65 nm Technology

Process" Journal of Nanoscience and Nanotechnology, ISSN: 1546-1955, Volume-16, Issue No: (5-6), Page No: 2628-2634, June 2019.

- 45. P Ramakrishna, K Hari Kishore "Implementation of Low Power and Area Efficient 7-Bit Flash Analog to Digital Converter" Journal of Nanoscience and Nanotechnology, ISSN: 1546-1955, Volume-16, Issue No: (5-6), Page No: 2213-2217, June 2019.

- 46. Ch. Naga Babu, P. Naga Siva Sai, Ch. Priyanka, K Hari Kishore, M. Bindu Bhargavi, K. Karthik "Comparative Analysis of High Speed Carry Skip Adders" International Journal of Engineering and Technology (UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.24, Page No: 121-125, April 2018.

- 47. G Siri Vennela, K Hari Kishore, E Raghuveera "High Accurate and Power Efficient ECG-Based Processor for Predicting Ventricular Arrhythmia" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 10, Issue No: 2, Page No: 1180-1121, May 2018.

- 48. P. Gopi Krishna, K. Sreenivasa Ravi, K Hari Kishore, K Krishna Veni, K. N. Siva Rao, R.D Prasad "Design and Development of Bi-Directional IoT gateway using ZigBee and Wi-Fi technologies with MQTT Protocol" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 125-129, March 2018.

- 49. Mahesh Madavath, K Hari Kishore "RF Front-End Design of Inductorless CMOS LNA Circuit with Noise Cancellation Method for IoT Applications" International Journal of Innovative Technology and Exploring Engineering, ISSN: 2278-3075, Volume-8, Issue No: 6, Page No: 176-183, April 2019.

- 50. K Divya Madhuri, K Hari Kishore "Implementation of 4-bit Ripple Carry Adder by Adopting Sub threshold Adiabatic Logic for Ultralow-Power Application" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 12, Issue No: 6, Page No: 11-17, May 2020.

- 51. Bhogadi Anil Kumar, Chillapalli Haritha, Gumpena Veda Sri Leela, E Raghuveera, K Hari Kishore" A Parametric DFT Scheme for RAMs" Journal of Advanced Research in Dynamical and Control Systems, ISSN No: 1943-023X, Vol No: 12, Issue No: 2, Page No: 2298-2305, May 2020.

- 52. A Murali, K Hari Kishore, G A Anitha Priyadarshini "Improved design debugging architecture using low power serial communication protocols for signal processing applications" International Journal of Speech Technology, ISSN No: 1572-8110, January 2021.

- 53. M. Kavitha, Zaid Hamid Mahmoud, Kakarla Hari Kishore, A.M. Petrov, Aleksandr Lekomtsev, Pavel Iliushin, Angelina Olegovna Zekiy, Mohammad Salmani "Application of Steinberg Model for Vibration Lifetime Evaluation of Sn-Ag-Cu based Solder Joints in Power Semiconductor" IEEE Transactions on Components, Packaging and Manufacturing Technology, P-ISSN: 2156-3950, E-ISSN: 2156-3985, January 2021.

- Hari Kishore Kakarla, Mukil Alagirisamy "Design of an Auto Adaption Unit for Reconfigurable Analog to Digital Converter" International Journal of Speech Technology, ISSN: 1572-8110, Volume-24, February 2021.