# Design of a Sobel Edge Detection Algorithm on FPGA

# Sudharshan K.M.<sup>1</sup>, PrashantV.Joshi<sup>2</sup>, Tresa Febina Francis<sup>3</sup>

<sup>1</sup>School of Electronics and Communications Engineering, REVA University, India <sup>2</sup>School of Electronics and Communications Engineering, REVA University, India <sup>3</sup>School of Electronics and Communications Engineering, REVA University, India <sup>1</sup>sudharshankm@reva.edu.in, <sup>2</sup>prashanthvjoshi@reva.edu.in, <sup>3r19mve22@ece.reva.edu.in</sup>

Article History: Received: 11 January 2021; Revised: 12 February 2021; Accepted: 27 March 2021; Published online: 23 May 2021

**Abstract**: In this paper we see the advantage to realize a real time parallel processing of image data comes with the use of Field Programmable Gate Array (FPGA). This paper highlights on the use of image edge detection, mainly turning the focus on a gradient filter, the Sobel filter. Here we design a Sobel edge detection algorithm to define the edge for a given gray scale image choosing the Zynq Development target board on Vivado software. Keywords:Digital Image,FPGA, Image processing, Sobel Edge Detection, Verilog.

### 1.Introduction

An image is a cluster, or a network of square pixels orchestrated in segments and lines. A picture is a twodimensional capacity f(x, y), where x and y are the spatial organizes. Image processing is a technique for improving raw images obtained from cameras/sensors installed on satellites, space tests, and flying machines, as well as images captured in everyday life for various applications. Image processing is widely classifies into two types namely, Analog image processing and Digital image processing. An example of analog image processing is change of a picture by electrical means. The television image is the most well-known illustration. The TV sign is a voltage level that varies in its ability to convey brilliance through the image. The appearance of the displayed picture is altered by electrically altering the sign. The splendor and complexity controls of a television set serve to regulate the quantity and reference of the video signal, resulting in the lighting up, and other effects.

As a subcategory or field of digital signal processing, digital image processing is the use of computer algorithms to perform image processing on digital images. Digital image processing has various advantages over analog image processing. It permits a much spacious range of algorithms to be applied to the input data and can be avoid problems such as the build-up of noise and signal distortion during processing. Since images are defined over multi dimensions digital image processing may be modelled in the form of multidimensional systems. There are various image enhancement techniques such as image smoothening, inversion, image contrast, image edge detection. The main focus here is edge detection. Edge detection is a procedure that senses the presence and location of borders constituted by crisp alterations in color, strength (or brightness) of an image. It can be proven that the discontinuities in image brightness are likely matching to discontinuities in deepness, discontinuities in surface orientation, alterations in stuff belongings and fluctuation in scene light. A two-dimensional filter and operators are used in a traditional method of edge detection. When the gradient in an image is the greatest, an edge appears. To find the edges, the operator identifies these large gradients. There are numerous operators designed to detect specific types of edges.

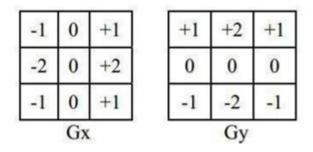

Edge detection can be accomplished in a variety of ways. In the process of developing the perfect edge detector, various edge detection algorithms have been developed. The majority, however, can be divided into two categories: gradient and Laplacian. The gradient method detects edges by looking for the maximum and minimum values in the image's first derivative. To find edges, the Laplacian method looks for zero crossings in the image's second derivative. On an image, the Sobel edge detector performs a 2D spatial gradient convolution operation. It computes the gradient in two directions using the convolution masks shown in. (i.e. row and column orientations).

A discrete differential operator is the Sobel operator. The operator employs two 3x3 kernels, one of which estimates the gradient in the x-direction and the other in the y-direction.

Figure 1: Sobel Operator uses 3x3 Kernel Masks

The image is convolved with both kernels to approximate the derivatives in horizontal and vertical change. At each given point, magnitude of the gradient can be approximated as in equation (1):

$$G = \sqrt{G_x^2 + G_y^2} \qquad (1)$$

#### 2. Literature survey

In reference [1], the edge detection architecture system contains two main modules, that is a 3 X 3 pixel generator and a sobel edge detection operation An 8 – bit pixel value of input is given to a 3 X 3 pixel generation block. This consists of two FIFO and 3 shift registers used for accumulation of valid input pixel data for processing.

Similarly in reference [2], the authors have explained the conventional sobel edge operation using two convolution kernels, which are vertical and horizontal filters. The proposed architecture makes use of four different kernels for better detection and gradient. The kernels are convolved together to obtain the gradient of the given image.

In reference [3], the images of different formats like .JPEG, .PNG, and .BMP are converted to obtain raw image data for processing. The image values ranges from 0 to 255. The extracted raw image data is then sent to FPGA in order to carry out mathematical operations. The communication between the computer and FPGA is established via parallel port which operates in a bidirectional mode.

The authors in [4] use an improved sobel edge detection with FPGA hardware that includes image input, gradient calculation block and threshold value processing block.

In reference[5] and [6], the authors utilize the two kernels where, the circuit is made up of two identical convolution blocks, one for the Gx operator and the other for the Gy operator. The circuit has clock (CK) and clear (CR) as inputs, along with one 16-bit output that represents the new image pixel after the filter is applied. It is made up of the following circuits: an address circuit, a data multiplexer circuit, a memory circuit, a control circuit, and a convolution circuit.

#### 3. Methodology

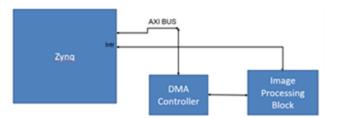

The system architecture comprises of the following blocks, DDR, Zynq PS, DMA controller and the image processing IP that holds the Sobel Edge detection algorithm. From the DDR, the pixel values of the digital image are streamed to the image processing IP which has been packaged on Vivado software, via the DMA controller. The controller reads the data through the AXI4 interface and sends it to the user IP through the AXI4 stream interface.

Figure 2: System Architecture

The stream IP processes the image, one or more pixel at a time depending on the streamed data width. The data width in this case will be 32 bit that is 4 pixels in parallel. After which the data is streamed back to the DMA controller. The controller receives the stream data from the IP and sends to the external DDR through AXI4 interface. The processed image is back in memory which can be sent to external interface or any display controller.

| -1 | -2 | -1 |   | -2  | -1 | 0 | -1  | 0 | l |  | 0    | 1  | 2 |  |

|----|----|----|---|-----|----|---|-----|---|---|--|------|----|---|--|

| 0  | 0  | 0  |   | -1  | 0  | 1 | -2  | 0 | 2 |  | -1   | 0  | 1 |  |

| 1  | 2  | 1  |   | 0   | 1  | 2 | -1  | 0 | 1 |  | -2   | -1 | 0 |  |

| 0° |    |    | , | 45° |    |   | 90° |   |   |  | 135° |    |   |  |

Figure 3: Convolution Kernels

The image processing IP is the block that does the gradient calculation. The proposed block uses four line buffers, a multiply and accumulate block, a design control and the output buffer block. In this paper, we are adding orientation by using four kernels and obtaining the processed image by convolving the four kernels together. Here pure streaming method cannot be used where the pixel values are scanned consecutively, hence we have adopted the unconventional method. Therefore we use buffers to access the three lines of data for 3 x 3 kernels. The line buffer size depends on the width of the image.[7]As soon as pixel values arrive in line buffers, the Sobel edge detection block can begin processing. The kernel gradients are calculated by reading eight pixels from line buffer. The obtained gradients are combined by adding their absolute values, and the edge map is computed by comparing the combined gradient to a threshold value.[8]Further work can be proceeded by implementing this on the FPGA board and display the edge detected image on a screen by use of a VGA controller.

## 4. Results

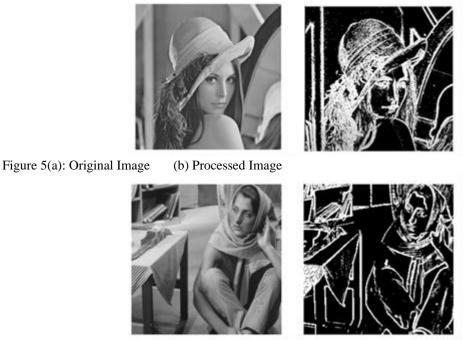

The digital image is saved in the simulation folder location for easy access and the packaged block is does it operation on the obtained image. Here we have taken grayscale images to test the block and have obtained the required processed image.

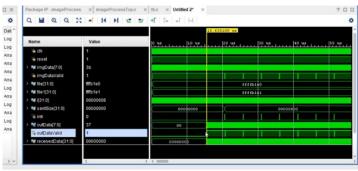

Figure 4: Waveform of the image processing block

Figure 6 (a): Original Image (b) Processed Image

## 5. Conclusion

This paper has the Sobel operator with increased orientation of the convolution kernels. Hence the operation block can locate edges accurately, thin the boundary lines and also not sensitive to noise. The sobel edge detection block is designed and obtained the processed images. The system architecture has been mapped on the software. The future scope would be to implement on the Zynq hardware and display the picture on a monitor using a VGA controller

## 6.Acknowledgements

The authors are gratefully acknowledge the facilities and support provided by the director of the school of Electronics And Communication Engineering of REVA UNIVERSITY, We also extend thanks to all teaching and non-teaching staff who had helped directly or indirectly to make this project successful.

## References

- A. Chaple and R. D. Daruwala, "Design of Sobel operator based image edge detection algorithm on FPGA," 2014 International Conference on Communication and Signal Processing, 2014, pp. 788-792, doi: 10.1109/ICCSP.2014.6949951.

- B. Z. Guo, W. Xu and Z. Chai, "Image Edge Detection Based on FPGA," 2010 Ninth International Symposium on Distributed Computing and Applications to Business, Engineering and Science, 2010, pp. 169-171, doi: 10.1109/DCABES.2010.39.

- C. Bhoyar, Sheetal D., Tarnnum Pathan, and Amit D. Landge. "Design and implementation of sobel edge detection technique using VHDL." International Journal of Advanced Research in Science, Engineering and Technology 3.5 (2016).

- D. Zhang, K., Zhang, Y., Wang, P., Tian, Y., & Yang, J. (2018). An improved sobel edge algorithm and FPGA implementation. Procedia computer science, 131, 243-248.

- E. D. Alghurair, S. S. AI-Rawi, "Design of Sobel Operator using Field Programmable Gate Array," in Proc. International Conference on Technological Advances in Electrical, Electronics and Computer Engineering (TAEECE), pp. 589-594, May 2013.

- F. O. Folorunso, O. R. Vincent, A, —A Descriptive Algorithm for Sobel Image Edge Detectionl, Proceedings of Informing Science &IT Education Conference, pp. 97-107, 2009.

- G. TIME BASED PERFORMANCE EVALUATION OF EXTRACTED PAVEMENT BITUMEN, Mahendra Umare, International Journal Of Advance Research In Science And Engineering http://www.ijarse.com IJARSE, Volume No. 10, Issue No. 05, May 2021 ISSN-2319-8354(E).

- H. Singh S, Saini A K, Saini R, et al. A novel real-time resource efficient implementation of Sobel operator-

based edge detection on FPGA [J]. International Journal of Electronics, 2014, 101(12):1705-1715.

I. AlAli, Mohammad I., Khaldoon M. Mhaidat, and Inad A. Aljarrah. "Implementing image processing algorithms in FPGA hardware." 2013 IEEE Jordan Conference on Applied Electrical Engineering and Computing Technologies (AEECT). IEEE, 2013.