# A New Speed Power Area and Accuracy (SPAA) Aware Cordic Processing Unit By VedicMathematics For The Application of Computer Vision

# Nitesh Kumar Sharma<sup>1</sup>, Dr. Shanti Rathore<sup>2</sup>, Dr. M. R. Khan<sup>3</sup>

<sup>1</sup>Electronics and Communication Engineering Dr.C.V. Raman University Bilaspur, India <sup>2</sup>Electronics and Communication Engineering Dr.C.V. Raman University Bilaspur, India <sup>3</sup>Electronics and Telecommunication Engineering Government Engineering College Jagdalpur, India <sup>1</sup>Sharma786.nitesh@gmail.com, <sup>2</sup>rathoreshanti@gmail.com, <sup>3</sup>mrkhan@gecjdp.ac.in

### Article History: Received: 11 January 2021; Accepted: 27 February 2021; Published online: 5 April 2021

Abstract—we are living in the era of fast processing applications like 3D, 5G, 9D. These types of application need a processing unit which have separate arithmetic unit & separate trigonometric unit which is well known as CORDIC processing unit. As we know Graphics processing unit is the brain of any graphics systems now a days there is Gaming specific systems are available which require ultra-high-speed GPU on those GPU there is separate trigonometric calculation processing unit is there which is called CORDIC. So, in this paper basically we proposed a novel architecture of CORDIC unit which is able to give the output in very less time. In this paper we also try to do the justice with the speed power area and accuracy Metrix.

Keywords—GPU, 3D, 5G, 9D, HD, ALU, SPAA

## 1. Introduction

Vedic Mathematic create a great support system for the fast calculation, by using of Vedic Mathematics we are able to get result in very few sec. As we know this is the era of high-speed internet, 4D graphics video, and 5G network. Now if you are talking about fast speed so there is need of fast calculation regarding that calculation, we can use Vedic mathematics.2020 is the period of high class clinical, aviation, robotization, and media innovation. According to these sort innovation there is necessity of acceptable nature of calculation which can do quick handling in exceptionally less time. As we probably am aware for sight and sound application now a days PC vision is assumed each significant part according to the PC vision, essentially it's a virtual vision framework which is show the fanciful substance in to this present reality. For these sort of high illustrations based PC vision there must be a need of extraordinary quality level based quick handling calculation which can make a quick preparing programming for those sort PC vision application. As we probably am aware every one of these calculations are dealing with preparing unit and according to the handling unit there is must be an Arithmetic unit is there which can do all sort of numerical figuring, presently the inquiry is just ALU unit is adequate to do quick handling for these sort of utilization and the appropriate response is no. According to the count of those sort of use need a Graphics handling unit where GPU have all unique kind of figuring measure. Presently CORDIC processor is one of the main calculations which are used in GPU for the count of mathematical capacities. In this paper we proposed a novel CORDIC processor which depends on estimate rationale, aside from that in this paper we did the correct similar examination on existing CORDIC calculation and Proposed CORDIC processor. According to the our relative examination on calculation level we utilize Discrete Cosine Transform based picture pressure calculation and play out the quality level investigation as far as picture quality boundaries.

The rest of the paper is sub arranged as follows. Important foundation and fundamental guideline of CORDIC Algorithm is given in Section II while Section III presents the Proposed CORDIC processor. Section IV presents the result analysis & comparative analysis Section V is end which wraps up the whole paper.

### 2. Literature Review

VLSI technology is a chip processing technology through VLSI now a days most of the applications are based on hardware. Where processing units are the most important part any application. In present era through VLSI there is possibility to create an application specific processing unit which is known as ASPU. Now if we are talking about any of the processing unit so the most important and common factor is its calculation unit which is known as ALU. Now a day's most of the applications have application specific arithmetic unit which is only design for that application only. Similar approximation logic is the one of the most important logic through this approach we are able to get application specific arithmetic unit. Now as we know Vedic mathematics is the one of the greatest and fast calculation mathematical approach. Using Vedic mathematics, we are able to get the value of any calculation logic in fraction of time. So now a days in VLSI Vedic mathematics play a great and most important role. If we are talking about the CORDIC so CORDIC is kind of application specific processing unit which is mostly design for high end graphics processing units as there are two type of arithmetic calculation, where first is simple arithmetic logic which require addition subtraction, multiplication & division. Apart from that another type of mathematical logic is trigonometric so now a day there is specifically another processing unit is using which is known as cordic processing unit. Now the history of CORDIC is started in 1959 [10]. As per this approach there is loads of extra calculation is require for the calculation of cosine & amp; sine. In [18], [19], [20] they makes use of the Taylor method and the usage of that logic they calculate the COSINE & amp; SINE value however the problem with this strategy is too lots time consumption due to the variety of new release process. Now after that scaling free cording is proposed by way of [23] the place they are the usage of a method which is now not the usage of scale however once more it's an generation process. Supriya [24] in accordance to this paper creator recommend an strategy which is terrific in time & amp; area. Supriya 2012[26]: This paper suggests a mechanical get mutually amazing game-plan for making backward of cosecant and secant waves task to the CORDIC (Coordinate Rotation Digital Computer) tally. In this outstanding shape the cordic experiences quintessential downsides like scale-factor figuring, slowness and satisfactory affirmation of little diploma turns. The requested figuring beats these weights. We make use of the use of one piece disclosure system to see the little increase turns. The scale free technique of the requested estimation relies upon upon on Taylor manner enhancement of the sine and cosine waves. Supriya 2013[27] this paper indicates a novel definitely sans scaling CORDIC figuring in upward shove up mode for hyperbolic heading. They use most-immense 1 piece ID strategy for limit as soon as extra scale flip enchancment age to scale once more the share of cycles. These are previous investigates which are recognized with the CORDIC figuring. As per the preceding present technological knowhow there is loads of enchancement is require right here we additionally see there is plenty of complexity in CORDIC processing unit. Many authors strengthen imprecise however simplified arithmetic units, which grant an more layer of strength financial savings over conventional low-power plan techniques. This is attributed to the decreased good judgment complexity of the proposed approximate arithmetic units. Note that the approximate arithmetic units no longer solely have decreased wide variety of transistors, however care is taken to make certain that the interior node capacitances are a good deal reduced. Due to the barriers in this techniques and the accuracy degree necessities nevertheless the complexity can be decreased and the SPAA (Speed Power, Area, Accuracy,) metrics can be nonetheless performed efficiently. So to enhance SPAA metrics we want a novel arithmetic unit with low power, excessive speed, with extended density and PVC conscious circuits.

#### 3. Methodology & Implementation

CORDIC algorithm is most powerful algorithm which used in GPU, due to that algorithm now a days we are able to get the great experiences on video & image processing system. As per the classic CORDIC algorithm they use the vector, Va[Xa, Yb] be derived via rotating the vector Vb[Xa, Yb] through an angle, then:

$$\begin{bmatrix} Xb\\ Yb \end{bmatrix} = Rp. \begin{bmatrix} Xa\\ Ya \end{bmatrix}, Rp = \begin{bmatrix} Cos\Theta - Sin\Theta\\ Sin\Theta & Cos\Theta \end{bmatrix}$$

(1)

Here equation (1) shapes the fundamental rule for iterative arrange calculation in CORDIC algorithm [1].

$$\Theta = \sum_{I=0}^{B} ui * ai$$

(2)

Here  $ui = -1,1$ ;  $ai = tan^{-1} 2^{-i}$

As we can see in equation (3), the scale issue Ki is free and no longer dependent of the direction of microrotation

$$Rp = Ki. \begin{bmatrix} 1 & -ui. \ 2^{-i}\theta \\ ui. \ 2^{-i} & Cos\theta 1 \end{bmatrix}$$

(3)

#### **Proposed Processing Unit:**

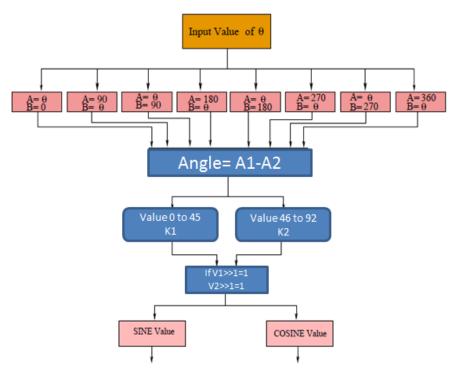

As per our proposed algorithm we basically follow the mathematical formula for the calculation of Sine & Cosine value, we perform the followings steps:

- 1. Angel Difference

- 2. Use of Vedic Multiplier

- 3. Modified Radian K1 (For Sin 0-45)

4. Modified Radian K2 (For Sin 46-90)

Fig.3.1 Proposed Design Flow

Using this way we calculate the value of sine & Cosine, as per this proposed algorithm we are able to get output, now for multiplication point of view use the approximate Vedic multiplier.

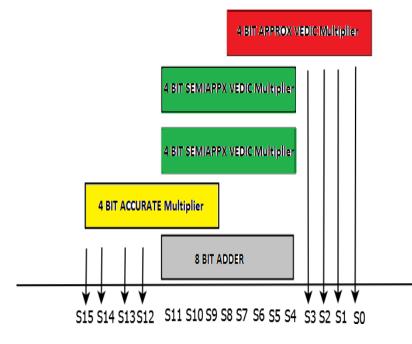

**Approximate Vedic Multiplier:** As per this multiplier use the concept of Urdhvatiryakbhyam, as per this design 4 BIT Accurate Urdhava multiplier, 4 Bit Semi Approximate Urdhava Multiplier and at last we design 4 Bit pure approximate Urdhava multiplier. According to Pure approximate multiplier our initial 4 bit is generated by the combination of 1,0. For Semi approximate our initial two is generated by 1,0 combination.

Fig. 3.2 8 Bit Approximate Multiplier

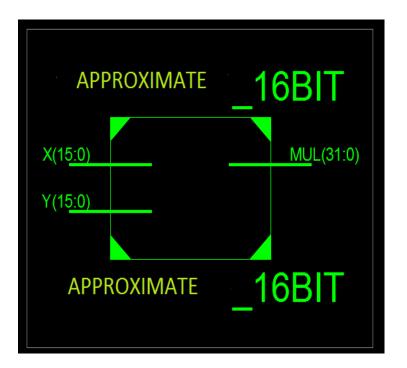

Figure 3.3 Schematic of Approximate Multiplier

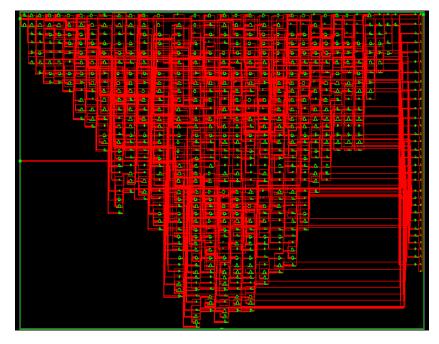

Figure 3.4LUT of Approximate Multiplier

So here we proposed a novel architecture for calculation of sine & cosine trigonometric functions.

Fig.3.5 Proposed Architecture

As we can see on fig. 3.5 its shows that out proposed architecture id follows the three steps which are:

- 1. Angel Calculation

- 2. Use of Vedic Multiplier

- 3. Calculation of K1 & K2

So as per the first step we calculate angel value by using of angel rotation concept. Once angel calculate than we calculate the K1 & K2 value by using of radian calculation where we apply the approximation logic & approximate Vedic Multiplier.

### 4. Result & Analysis

In this section we are doing the comparative analysis based on different kind of parameters.

In this part we introduce the relative investigation of all with previous existing methodology. For analysis factor of view we use these parameters:

- 1. Power

- 2. Speed

- 3. Hardware (LUT)

- Here we use FPGA technology:

- 1. Spartan 3

- 2. Spartan 6

- 3. Spartan 7

- 4. FSIM

# **Table 4.1 Error Analysis**

| Θ       | CORDIC | Scaling<br>Free | Efficient<br>CORDIC | Taylor<br>Based | Proposed |

|---------|--------|-----------------|---------------------|-----------------|----------|

| 0-90    | 0      | 0-0.008         | 0-0.009             | 0-0.01          | 00-0.007 |

| 90-180  | 0      | 0-0.006         | 0-0.008             | 0-0.008         | 0-0.007  |

| 180-270 | 0      | 0-0.036         | 0-0.00256           | 0-0.009         | 0-7      |

| 270-360 | 0      | 0-0.096         | 0-0.002369          | 0-0.008         | 0-0.007  |

## **Comparative Multiplier Analysis:**

Approximate Multiplier Accuracy Level is 85-90%. The FPGA comparison analysis of approximate and accurate are shown below, here hardware analysis is done on Vertex 6 FPA which is 45nm based technology.

As per the correlation table obviously approximate multiplier in more productive to utilize in light of the fact that it has less deferral as contrast with other multiplier. Less postpone that implies when rough multiplier has utilize then processor result will be get in a couple of Nano/Pico seconds. This multiplier likewise have less LUT Logic implies this is a less cost multiplier and the recurrence Column of the table is demonstrating that it recurrence are Very high as contrast with other multiplier.

## **Comparative Proposed Vedic CORDIC Processing Unit:**

| Table 4.2 Reasonable Time Analysis |          |           |          |          |  |

|------------------------------------|----------|-----------|----------|----------|--|

| FPGA                               | Taylor   | Efficient | Scaling  | Proposed |  |

| TYPE                               | Based    | CORDIC    | Free     |          |  |

|                                    |          |           |          |          |  |

| Spartan 3                          | 140.52us | 120.33us  | 135.63us | 110.25us |  |

| Spartan 6                          | 97.25us  | 77.67us   | 80.32us  | 68.62us  |  |

| Spartan 7                          | 65.42us  | 54.56us   | 58.86us  | 52.56us  |  |

# Table 4.2 Reasonable Time Analysis

| S.NO. | Multiplier<br>Name | LUT | Delay  | Frequency |  |

|-------|--------------------|-----|--------|-----------|--|

| 1     | Add_Shift          | 591 | 7.29   | 137.17    |  |

| 2     | Wallace Tree       | 504 | 10.591 | 94.41     |  |

| 3     | Urdhav             | 441 | 7.299  | 137       |  |

| 4     | BWSM               | 413 | 9.102  | 109.86    |  |

| 5     | BOOTH              | 536 | 7.536  | 132.69    |  |

| 6     | Approximate        | 364 | 6.998  | 142.89    |  |

#### Table 4.3 Reasonable Multiplier Analysis

### Table 4.4Reasonable Power Analysis

| FPGA<br>TYPE | Taylor<br>Based | Efficient<br>CORDIC | Scaling<br>Free | Proposed |

|--------------|-----------------|---------------------|-----------------|----------|

| Spartan 3    | 1.823mw         | 1.325mw             | 1.51 mw         | 1.35mw   |

| Spartan 6    | 1.057mw         | 0.826 mw            | 0.946<br>mw     | 0.722mw  |

| Spartan 7    | 0.699mw         | 0.502mw             | 0.560mw         | 0.185mw  |

**Table 4.5 Comparative LUT Analysis**

| FPGA<br>TYPE | Taylor<br>Based | Efficient<br>CORDI | Scaling<br>Free | Proposed |

|--------------|-----------------|--------------------|-----------------|----------|

| Spartan 3    | 247             | 197                | 207             | 178      |

| Spartan 6    | 127             | 93                 | 106             | 87       |

| Spartan 7    | 85              | 62                 | 73              | 58       |

In terms of architecture level analysis our proposed approach is far better than with others.

# **Comparative Analysis:**

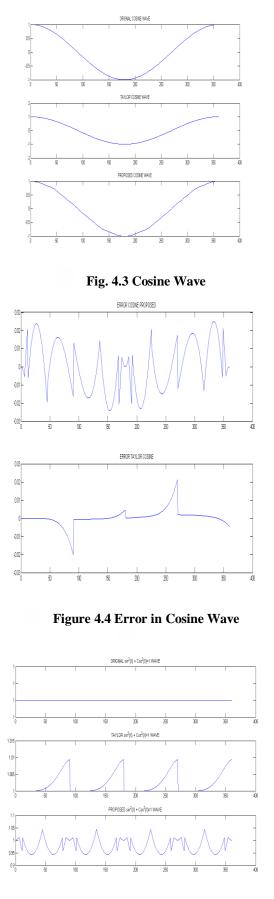

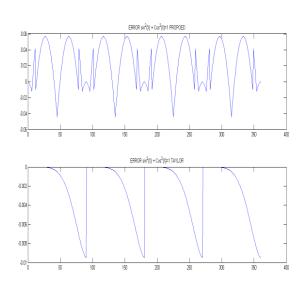

Using the sin and cosine I have analyzed the error difference between the sin wave and cosine individually and Trigonometric Identities  $\sin^2(x) + \cos^2(x) = 1$  after analyzing the results in conventional approach, the results:

Figure 4.1 Sine Wave

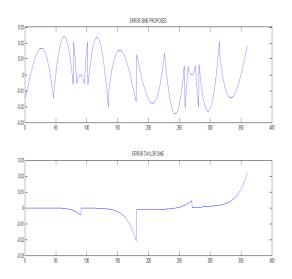

Figure 4.2 Error In Sine Wave

Figure 4.5Trigonometric Identities

Figure 4.6 Trigonometric Identities Error

## 5. Conclusion

CORDIC is an effective algorithm, and a famous algorithm of preference when it comes to a number Digital Signal Processing applications. Implementation of a CORDIC-based processor on FPGA gives us a effective mechanism of imposing complicated computations on a platform that affords a lot of assets and flexibility at a rather lesser cost. Further, given that the algorithm is easy and environment friendly the graph and VLSI implementation of a CORDIC primarily based processor is without problems achievable. According to cutting-edge development future is definitely hooked up on digital world. Right now every lessens depends upon on-line like shopping, films, pictures, instructions assessed time of appearance. So for these type of use there is want of some different stable gadget which are recognized as communitarian structure, arranging, Internet of things, etc. As we probable am conscious cordic dealing with unit is essentially produce from the cordic calculation, it implies if cordic calculation is fine as some distance as calculation boundaries with the purpose that strategy will be desirable as a long way as the engineering level. Here we use the VLSI science to construct a CORDIC processing uni , on that evaluation we create processing unit on more than one FPGA like Virtex 4, Virtex 6 & amp; Virtex 7 and primarily based on the comparative evaluation we discovered our proposed structure I a ways higher than in phrases of velocity strength & amp; area. Our proposed machine proper makes a justice with the SPAA matrix. As per propped strategy we are in a position to get the enhancement of 20-25%.

### References

- 1. Barozzi, Sara, et al. "Filtering images extracted from social media in the response phase of emergency events." 16th Conference on Information Systems for Crisis Response and Management. 2019.

- 2. Parmar, Yashrajsinh, and K. Sridharan. "A Resource-Efficient Multiplierless Systolic Array Architecture for Convolutions in Deep Networks." IEEE Transactions on Circuits and Systems II: Express Briefs (2019).

- 3. Gurantz, Itzhak, Yoav Goldenberg, and Sree A. Raghavan. "Demodulator for consumer uses." U.S. Patent No. 5,550,869. 27 Aug. 1996.

- Wang, Sicong, Zhiping Wen, and Lixin Yu. "High-performance fault-tolerant CORDIC processor for space applications." 2006 1st International Symposium on Systems and Control in Aerospace and Astronautics. IEEE, 2006.

- 5. Huang, Yi, Zhi-Qian Yang, and Li-Jun Guo. "Application of CORDIC algorithm in processing of tethered pose of aerostat radar [J]." Journal of Hefei University of Technology (Natural Science) 11 (2010).

- 6. Hore, Alain, and Djemel Ziou. "Image quality metrics: PSNR vs. SSIM." 2010 20th International Conference on Pattern Recognition. IEEE, 2010.

- 7. Zhang, Lin, Lei Zhang, and Xuanqin Mou. "RFSIM: A feature based image quality assessment metric using Riesz transforms." 2010 IEEE International Conference on Image Processing. IEEE, 2010.

- 8. Zhang, Lin, et al. "FSIM: A feature similarity index for image quality assessment." IEEE transactions on Image Processing20.8 (2011): 2378-2386.

- 9. J. E. Volder, The CORDIC Trigonometric Computing Technique, IRE Trans. Elec-tronic Computing, Vol. EC-8, Sept 1959, pp. 330- 334.

- J. S.Walther, A unified algorithm for elementary functions, Spring Joint ComputerConf., 1971, Proc., pp. 379-385.

- 11. S. F. Hsiao, Y. H. Hu and T. B. Juang, A Memory Efficient and High SpeedSine/Cosine Generator Based on Parallel CORDIC Rotations, IEEE Signal Pro-cessing Letters, Vol. 11, No.2, Feb-2004, pp. 152-155

- 12. N. Takagi, T. Asada, and S. Yajima, Redundant CORDIC methods with a constantscale factor for sine and cosine computation, IEEE Trans. Computers, vol. 40, pp.989995, Sept. 1991.

- 13. K. Maharatna and S. Banerjee, A VLSI array architecture for hough transform, Pattern Recognit., vol. 34, pp. 15031512, 2001.

- K. Maharatna, A. S. Dhar, and S. Banerjee, A VLSI array architecture for real-ization of DFT, DHT, DCT and DST, Signal Process., vol. 81, pp. 18131822,2001.

- 15. Y. H. Hu and H. M. Chern, VLSI CORDIC array structure implementation of Toeplitz eigensystem solvers, in Proc. IEEE Int. Conf. Acoust. Speech, Signal Processing, NM, 1990, pp. 15751578.

- Pramod K. Meher, Javier Walls, Tso-Bing Juang, K. Sridharan, Koushik Ma-haratna, 50 Years of CORDIC : Algorithms, Architectures and Applications, IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 56, No. 9, Sept.2009, pp. 1893- 1907.

- 17. C. S. Wu and A. Y. Wu, Modified vector rotational CORDIC (MVR-CORDIC )algorithm and architecture, IEEE Trans. Circuits Syst. II, vol. 48, pp. 548561,June, 2001

- Cheng-Shing Wu, An-Yeu Wu and Chih-Hsiu Lin, A High- Performance/Low-Latency Vector Rotational CORDIC Architecture Based on Extended Elementary Angle Set and Trellis-Based Searching Schemes, IEEE Transcations on Circuits and SystemsII : Analog and Digital Signal Processing, Vol. 50, pg. 589601, No. 9,Sept. 2003.

- 19. Y. H. Hu and S. Naganathan, An angle recoding method for CORDIC algorithm implementation, IEEE Trans. Computers, vol. 42, pp. 99–102, Jan. 1993.

- K. Maharatna, S. Banerjee, E. Grass, M. Krstic, and A. Troya, Modified virtually scaling-free adaptive CORDIC rotator algorithm and architecture, IEEE Trans. Circuits Syst. Video Technol., vol. 11, no. 11, pp. 14631474, Nov. 2005.

- K. Maharatna, A. Troya, S. Banerjee, and E. Grass, Virtually scaling free adaptive CORDIC rotator, IEE Proc.-Comp. Dig. Tech., vol. 151, no. 6, pp. 448456, Nov.2004.

- 22. Leena Vachhani, K. Sridharan and Pramod K. Meher, Efficient CORDIC Algo-rithms and Architectures for Low Area and High Throughput Implementation, IEEE Transactions on Circuit and SystemsII: Express Briefs, Vol. 56, No. 1, pg.61-65., January 2009.

- 23. F.J. Jaime, M. A. Sanchez, J. Hormigo, J. Villalba and E. L. Zapata, "Enhanced scaling-free CORDIC," IEEE Trans. Circuits and Systems I: Regular Papers, Vol.57 No.7, pp. 1654-1662. July 2010.

- Aggarwal, S.; Meher, P.K.; Khare, K., "Area-Time Efficient Scaling-Free CORDIC Using Generalized Micro-Rotation Selection," Very Large Scale Integration (VLSI)Systems, IEEE Transactions on , vol.20, no.8, pp.1542,1546, Aug. 2012 doi:10.1109/TVLSI.2011.2158459

- Causo, M.; Ting An; Alves de Barros Naviner, L., "Parallel scaling-free and area-time efficient CORDIC algorithm," Electronics, Circuits and Systems (ICECS),2012 19th IEEE International Conference on , vol., no., pp.149,152, 9-12 Dec.2012 doi: 10.1109/ICECS.2012.6463778

- 26. Aggarwal, S.; Khare, K., "Hardware Efficient Architecture for Generating Sine/Cosine Waves," VLSI Design (VLSID), 2012 25th International Conference on , vol.,no.,pp.57,61,7-11Jan.2012

- Aggarwal, S.; Meher, P.K.; Khare, K., "Scale-Free Hyperbolic CORDIC Processor and Its Application to Waveform Generation," Circuits and Systems I: Regular Papers, IEEE Transactions on , vol.60, no.2, pp.314,326,Feb.2013

- 28. J. Vankka, Digital Synthesizers and Transmitters for Software Radio, Dordrecht, Netherlands. Springer: 2005.

- Maher Jridi, Ayman Alfalou. Direct Digital Frequency Synthesizer with CORDIC Algorithm and Taylor Series Approximation for Digital Receivers. European Journal of Scientific Research, EuroJournals, 2009, 30 (4), pp.542-553. ffhal-00516790f

- Honey Durga Tiwari, Ganzorig Gankhuyag, Chan Mo Kim, Yong Beom Cho, "Multiplier design based on ancient Indian Vedic Mathematics," IEEE International SoC Design Conference Vol. 02, 2008, pp.: II-65 -II-68.

- 31. Jagadguru Swami Sri Bharath, Krisna Tirathji, Vedic Mathematics or Sixteen Simple Sutras From The Vedas, Motilal Banarsidas, Varanasi(India),1986.

- 32. Sivanandam K and Kumar P, "Run time reconfigurable modified Vedic multiplier for high speed multimedia applications," 2015 2nd International Conference on Computing for Sustainable Global Development (INDIACom), New Delhi, 2015, pp. 2109-2113.

- 33. Nitesh Kumar Sharma, Dr. Shanti Rathore, and Dr. M.R. Khan "A Comparative Analysis on Coordinate Rotation Digital Computer (CORDIC) Algorithm and Its use on Computer Vision Technology," First International Conference on Power, Control and Computing Technologies, 2020, pp., 106-110.

- 34. Parth Mehta, Dhanashri Gawali "Conventional versus Vedic mathematical method for Hardware implementation of a multiplier" International

- 35. Conference on Advances in Computing, Control, and Telecommunication Technologies- pp. 640-642, 2009.

- 36. Anvesh kumar et. all "Small area Reconfigurable FFT Design by Vedic Mathematics" vol(5), pp.836-838, 2010.

- 37. Devika Jain, Kabiraj Sethiand Rutuparana Panda "Vedic Mathematics Based Multiply Accumulate Unit" International Conference on Computational

- 38. Intelligence and Communication Systems, pp.754-757, 2011.

- 39. Nitesh Kumar Sharma, Deepesh Kumar Gautma, M.R. Khan "A Comparative Analysis on Multiplier." International Conference on Computing, Communication and Networking Technologies 2020.