# Implementation in Direct Digital Synthesizers (DDS) Based on CORDIC Algorithm

## Nitesh Kumar Sharma<sup>1</sup>, Dr. M. R. Khan<sup>2</sup>, Dr. Jainendra Jain<sup>3</sup>

<sup>1</sup>Electronics and Communication Engineering Dr.C.V. Raman University Bilaspur, India <sup>2</sup>Electronics and Telecommunication Engineering Government Engineering College Jagdalpur, India <sup>3</sup>Mathematics Government Engineering College Jagdalpur, India Sharma786.nitesh@gmail.com<sup>1</sup>, mrkhan@gecjdp.ac.in<sup>22</sup>, jainendrajain@gecjdp.ac.in<sup>3</sup>

Article History: Received: 11 January 2021; Accepted: 27 February 2021; Published online: 5 April 2021

Abstract: The universality of computerized signal handling (DSP) has made expanding request to create territory effective and precise structures in completing numerous nonlinear math tasks. One such design is CORDIC unit which has numerous applications in the field of DSP including actualizing changes dependent on Fourier premise. This paper offers structure of CORDIC, inserted with a pipelined unit that has exclusively negligible scope of adders and shifters. It tends to be applied in pivot mode as appropriately as vectoring mode. The reason for the arrangement is to get a pipelined CORDIC unit keeping up the format of valid calculation. Preparing and discussion structures work CORDIC in round organize contraption and in both of pivot or vectoring modes. **Keywords:** Trigonometry, CORDIC, FPGA, DCT, Fourier Transform

## 1. Introduction

Organize Rotation Digital Computer (CORDIC), an unmistakable explanation PC to process numerous non-straight and supernatural capacities, used to be proposed by utilizing Volder in 1959 [9]. The highlights that can be registered the utilization of a CORDIC PC comprise of trigonometric, logarithmic, exponential, hyperbolic, duplication, division, rectangular root, and so forth [10]. Despite the fact that it toward the beginning served the explanation of route frameworks, it later developed to be a well-known gadget to place into impact many computerized structures specifically in the zones of advanced sign handling, correspondences, PC designs, and so forth [20]. The effortlessness of CORDIC is that it can figure any of the above alluded to highlights the utilization of movements and increments which are of the structure the working mode and the arrange gadget picked are two key components to register the supported highlights in the CORDIC. Many sign handling and discussion structures work CORDIC in round organize device and in both of revolution or vectoring modes.

### 2. Literature Review

An embedded system is a hardware computer system that is dedicated to specific functions to serve in a larger mechanical or electrical system when response time is the primary concern. Embedded systems are very general purpose systems due to its qualities like low power consumption and economical low cost. The micro-controller and DSP, embedded systems has the disadvantage of instruction execution, it executes the instruction sequentially [27], [28]. The sequential execution starts which fetches the instruction appended by decoding an execution. After fetching it starts fetching the next code while decoding the previous code. So it is inherently a sequential system that will take more clock cycle to execute an algorithm. So our primary goal is to develop a hardware that executes an algorithm with less number of clock cycles. This facility is available in FPGA platform. A field-programmable gate array (FPGA) is an integrated circuit designed which can be arranged by a client or a designer subsequent to assembling, consequently "fieldprogrammable", which is the most favorable advantage of FPGA over micro-controller. We can have the processes done according to the written HDL code "in parallel" which means simultaneously. The ability of FPGA parallel processing is one of the most important features that separate FPGA from theprocessors and made it superior in many areas. This facility is adopted in our work. The image processing techniques are validated using some high-level languages that will increase the bugged, and the algorithms are also sequential. Embedded micro-controller can be a better choice for design and economic cost system. From the above discussion, we have concluded that, for real-time operation the embedded system like microcontroller and DSP, not a right choice for real-time image processing system [20][24]. FPGA platform is giving a better advantage to implementing the sequential image processing algorithms in the parallel platform. The FPGA hardware works as shown below. In FPGA, the processes are concurrent means the produces output simultaneously. So the algorithms can process in parallel. Due to this advantage in FPGA we chose FPGA as the hardware platform.

It seen from sampling theorem, that the representation of the sparse signal in some basis of the dictionary is possible with less number of coefficients. DCT is a commonly used sparse representation

dictionary for image signal in the frequency domain. So, it can help to reduce the memory allocation for storing the signal for further use as in JPEG. Also, it reduces the bandwidth of channel. So it will be very convenient that if we can find the information about the image in DCT domain, then we can analyze that this image is acceptable for display or not. DCT is a unitary transform, and it obey the Parseval theorem. Using this property and SSIM spatial equation, the relation between spatial components in terms of DCT coefficients can be found out. To speed up the operation, it is required to do some parallel architecture to find SSIM in DCT domain. So the assessment of distortion of the image in DCT domain is possible. So we can calculate the SSIM in DCT domain.

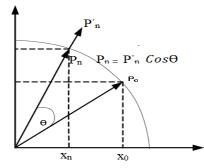

The rotation of a two dimensional vector with an angle  $\theta$ , to obtain a final rotatedvector. Here the initial vector and rotated final vector are  $P_0 = [x_0, y_0]$  and  $P_n = [x_n, y_n]$

$P_n = RP_0P_{n=} P'_n \text{ Cos}\theta$

Fig.1 Graphical Representation of CORDIC

Where R is given as

$$R = \begin{bmatrix} Cos\theta - Sin\theta\\ Sin\theta & Cos\theta \end{bmatrix}$$

(1)

Also write as

$$R = [1 + \tan^2 \theta] X \begin{bmatrix} 1 & -\tan \theta \\ 1 & \tan \theta \end{bmatrix}$$

(2)

Where

$$R = K_{p}R_{p}$$

$$K_{p} = [1 + \tan^{2}\theta]$$

$$R_{p} = \begin{bmatrix} 1 & -\tan\theta \\ 1 & \tan\theta \end{bmatrix}$$

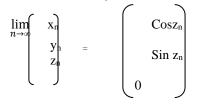

**3.1** Calculation of Cosine and Sine Function using CORDIC Algorithm

So, if we put some specific values in above equation sine and cosine function. The final output as sine and cosine function is calculated below. Where  $x_0 = K$ ,  $y_0 = 0$  and  $x_0 = \theta$  is taken.

Calculation of cosine and sine function has been validated with MATLAB. From the above simulation, it concludes that using this algorithm a core can be developed to calculate cosine and sine function. In this work,

we are considering only the cosine function so we developed core that will produce only cosine output for a particular input. So the cosine core is designed.

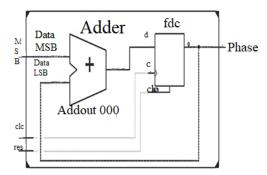

### **3.1 Proposed Methodology**

As referenced before, the proposed plan of DDS depends on pipelined CORDIC, which goes about as stage to sufficiency converter. The stage aggregator has an exactness of bits, which compares to that of the information, which is recurrence control word. The yield of stage gatherer is given as contribution to planned CORDIC square, which has a planning component that maps the pipelined CORDIC over the whole  $2\pi$  territory. The planning instrument works by considering the three hugest bits of the sources of info. That is, contingent upon the estimations of the three MSBs, the points are referenced in one of the eight octants. Figure 2 shows the stage collector schematic of proposed plan.

Phase Accumulator

Fig.2 Proposed Phase Accumulator

The moving in moderate stages in the proposed structure is made designed, along these lines improving inactivity and lessening the deferral of the plan. The check yield of the top module guarantees the right addition of the aggregation step. In the proposed plan, the sufficiency is spoken to utilizing input bits. In this way, the absolute number of plenty fullness quantization levels since the most noteworthy piece speaks to the indication of the abundancy. There are two yields of the proposed structure relating to the quadrature yields of sine and cosine. Consequently, the proposed structure creates quadrature yields utilizing single design. All in all, the data sources and yields of the proposed plan are recurrence control word for setting the yield recurrence, clock for setting testing recurrence, quadrature waves and check signal for checking aggregation file.

### 5. Conclusion

With standing that, the proposed plan produces quadrature yields which have better stage coordinate subsequently making the structure more valuable for the vast majority of the correspondence frameworks. The straightforward structure of DDS dependent on CORDIC consistently is a superior decision since actualizing this in circuits, for example, blenders, advanced down/up converters is less complex as far as equipment use. The higher the stage collector information width, the lesser is the stage quantization blunder. Henceforth, abundance exactness of the yield waveforms is improved. The most extreme recurrence of activity is 155.751 MHz. The cut postpone result of the proposed plan is 2.45. The complete force utilization of the proposed structure at the most extreme recurrence of activity is 638.61mW.

#### References

- 1. Barozzi, Sara "Filtering images extracted from social media in the response phase of emergency events." 16th Conference on Information Systems for Crisis Response and Management. 2019.

- 2. Parmar, Yashrajsinh, and K. Sridharan. "A Resource-Efficient Multiplierless Systolic Array Architecture for Convolutions in Deep Networks." IEEE Transactions on Circuits and Systems II: Express Briefs 2019.

- 3. Gurantz, Itzhak, Yoav Goldenberg, and Sree A. Raghavan. "Demodulator for consumer uses." U.S. Patent No.5, Aug. 1996, pp.550, 869.

- Wang, Sicong, Zhiping Wen, and Lixin Yu. "High-performance fault-tolerant CORDIC processor for space usage." 2006 1st International Symposium on Systems and Control in Aerospace and Astronautics. IEEE, 2006.

- 5. Huang, Yi, Zhi-Qian Yang, and Li-Jun Guo. "Usage of CORDIC algorithm in processing of tethered pose of aerostat radar [J]." Journal of Hefei University of Technology (Natural Science) 11 (2010).

- 6. Hore, Alain, and Djemel Ziou. "Image quality metrics: PSNR vs. SSIM."TwentiethInternational

Conference on Pattern Recognition. IEEE, 2010.

- 7. Zhang, Lin, Lei Zhang, and Xuanqin Mou. "RFSIM: A feature based image quality assessment metric using Riesz transforms." International Conference on Image Processing. IEEE, 2010.

- 8. Zhang, Lin, "FSIM: A feature similarity index for image quality assessment." IEEE transactions on Image ProcessingAug. 20111pp. 2378-2386.

- 9. J.E. Volder,"The CORDIC Trigonometric Computing Technique" IRE Trans. Electron. Computers," vol. EC-8, Sept 1959, pp. 330- 334.

- J. S.Walther, "A unified algorithm for elementary functions," Spring Joint Computer Conf., 1971, pp. 379-385.

- 11. S. F. Hsiao, Y. H. Hu and T. B. Juang, "A Memory Efficient and High SpeedSine/Cosine Generator Based on Parallel CORDIC Rotations," IEEE Signal Pro-cessing Letters, vol. 11, No.2, Feb-2004, pp. 152-155.

- 12. Aarti Ranji, Nashrah Fatima and Paresh Rawat "Area efficient VLSI architecture for DCT using modified CORDIC algorithm" International Conference on Emerging Technological Trends 2016.

- 13. N Prasad, Ayas Kanta Swain and K. K. Mahapatra "Design and error analysis of a scale free CORDIC unit with corrected scale factor" Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics, 2012.

- 14. Abhishek Mankar, N Prasad, Ansuman Dipti Sankar Das and Sukadev Meher. " Multiplierless VLSI architectures for radix-2 folded pipelined complex FFT core " International Journal of Circuit Theory and Applications, 2015.

- 15. Baozhou Zhu, Yuanwu Lei, Yuanxi Peng and Tingting He. "Low Latency and Low Error Floating-Point Sine/Cosine Function Based TCORDIC Algorithm" IEEE Transactions on Circuits and Systems I: Regular Papers, 2017.

- 16. N. Takagi, T. Asada, and S. Yajima, "Redundant CORDIC methods with a constantscale factor for sine and cosine computation," IEEE Trans. Computers, vol. 40,Sept 1991, pp.989-995.

- 17. K. Maharatna and S. Banerjee, "A VLSI array architecture for hough transform," Pattern Recognit., vol. 34, 2001,pp. 1503-1512.

- 18. K. Maharatna, A. S. Dhar, and S. Banerjee, "A VLSI array architecture for realization of DFT, DHT, DCT and DST," Signal Process., vol. 81, 3- 1822.

- 19. Y.H. Hu and H. M.Chern, "VLSI CORDIC array structure implementation of Toeplitz eigensystem solvers," in Proc. IEEE Int. Conf. Acoust. Speech, Signal Processing, NM,1990, pp. 1575-1578.

- Pramod K. Meher, Javier Walls, Tso-Bing Juang, K. Sridharan and Koushik Maharatna, "50 Years of CORDIC: Algorithms, Architectures and Usage," IEEE Transactions on Circuits and Systems-I: Regular Papers, Vol. 56, No.9, Sept.2009, pp. 1893-1907.

- 21. C. S. Wu and A. Y. Wu, "Modified vector rotational CORDIC (MVR-CORDIC) algorithm and architecture," IEEE Trans. Circuits Syst.II, vol.48,June 2001 pp. 548-561.

- 22. Cheng-Shing Wu, An-Yeu Wu and Chih-Hsiu Lin,"A High- Performance/Low- Latency Vector Rotational CORDIC Architecture Based on Extended Elementary Angle Set and Trellis-Based Searching Schemes," IEEE Transcations on Circuits and SystemsII : Analog and Digital Signal Processing, Vol.50,No.9, Sept. 2003,pp.589-601.

- 23. Y. H. Hu and S. Naganathan, An angle recoding method for CORDIC algorithm implementation, IEEE Trans. Computers, vol. 42, Jan. 1993, pp. 99–102.

- K. Maharatna, S. Banerjee, E. Grass, M. Krstic, and A. Troya, Modified virtually scaling-free adaptive CORDIC rotator algorithm and architecture, IEEE Trans. Circuits Syst. Video Technol., vol. 15, no. 11, Nov. 2005, pp. 1463-1474.

- 25. K.Maharatna, A.Troya, S.Banerjee, and E. Grass, "Virtually scaling free adaptive CORDIC rotator," IEE Proc.-Comp. Dig. Tech., vol.-151, no.6, Nov.2004, pp. 448- 456.

- Leena Vachhani, K. Sridharan and Pramod K. Meher, "Efficient CORDIC Algorithms and Architectures for Low Area and High Throughput Implementation," IEEE Transactions on Circuit and Systems-II,vol. 56, No. 1, January 2009, pp.61-65.

- 27. F.J. Jaime, M. A. Sanchez, J. Hormigo, J.Villalba and E. L. Zapata,"Enhanced scaling-free CORDIC," IEEE Trans. Circuits and Systems-I: Regular Papers, vol.57,No.7, July 2010pp. 1654-1662.

- 28. L. Cordesses, "Direct Digital Synthesis: A Tool for Periodic Wave Generation (Part 1)," IEEE Signal Processing Magazine, vol. 21, no. 4, pp. 50–54, Jul. 2004

- 29. Supriya Aggarwal, P.K Meher and K. Khare "Area-Time Efficient Scaling-Free CORDIC Using Generalized Micro-Rotation Selection,"IEEE Transactions onVery LargeScaleIntegration(VLSI)Systems,Vol.20,No.8,August2012,pp.1542-1546.

- 30. Matteo Causo, Ting an and Alves de Barros Naviner "Parallel scaling-free and area-time efficient CORDIC Algorithm," 19th IEEE International Conference on Electronics, Circuits and Systems, 2012, pp.149-152.

- 31. Supriya Aggarwal and K. Khare, "Hardware Efficient Architecture for Generating Sine/Cosine Waves,"25th International Conference on VLSI Design 2012.

- 32. S. Aggarwal, P.K Meher and K. Khare,"Scale-Free Hyperbolic CORDIC Processor and Its Usage to Waveform Generation," IEEE Transactions on Circuits and Systems-I, vol.60, No.2, 2013, pp.314-326.

- 33. J. Vankka, "Digital Synthesizers and Transmitters for Software Radio," Dordrecht, Netherlands. Springer: 2005.

- 34. Maher Jridi and Ayman Alfalou. "Direct Digital Frequency Synthesizer with CORDIC Algorithm and Taylor Series Approximation for Digital Receivers," European Journal of Scientific Research, Euro Journals, vol 30 (4), 2009, pp.542-553.

- 35. Nitesh Kumar Sharma, Dr. Shanti Rathore and Dr. M.R. Khan "A Comparative Analysis on Coordinate Rotation Digital Computer (CORDIC) Algorithm and Its use on Computer Vision Technology," First International Conference on Power, Control and Computing Technologies, 2020, pp., 106-110.

- 36. Nitesh Kumar Sharma, Shanti Rathore and M.R. Khan "CV(Computer Vision) System By Cordic Processing Unit" Journal Of Critical Reviews Vol.7(18),2020, pp.2235-2241.