# Scale Factor and Latency Analysis in CORDIC Processing Unit

## Nitesh Kumar Sharma<sup>1</sup>, Dr. Shanti Rathore<sup>2</sup>, Dr. Jainendra Jain<sup>3</sup>

<sup>1</sup>Electronics and Communication Engineering Dr.C.V. Raman University Bilaspur, India <sup>2</sup>Electronics and Communication Engineering Dr.C.V. Raman University Bilaspur, India <sup>3</sup>Mathematics Government Engineering College Jagdalpur, India

<sup>1</sup>Sharma786.nitesh@gmail.com, <sup>2</sup>rathoreshanti@gmail.com, <sup>3</sup>jainendrajain@gecjdp.ac.in

Article History: Received: 11 January 2021; Accepted: 27 February 2021; Published online: 5 April 2021

**Abstract**—Virtual laptop, cordic or synchronized, is a fast, quick, environmentally friendly algorithm for many applications used for the processing of digital signs. It typically uses an exquisite computing technique for the fixation of the trigonometrically relationships worried aboutrotation around plane coordinates and rectangular to polar shapeconversion, developed for actual airborne calculations. It contains a one-of-a-kind serial mathematics unit having 3 shift registers, 3 adders/sub tractors, appearance-up table and remarkable interconnections. Keywords—CORDIC, HDL FPGA, DCT, Latency

## 1. Introduction

For an extended time the neighborhood of digital signal processing has been dominated with the useful resource of manner of the manner of microprocessors. This speaks widely because of the fact that designers are given the blessing of multiple-cycle coaching, in particular, as one-of-a-kind approaches. Although these processors are much less comfortable and bendy, they can also be the incremental alternative when it comes to carrying out tasks such as fine upsetting signal processing. Compression of images, video editing and interactive conversation. The internal area of VLSI and IC architecture was developed rapidly with late characteristics. As a result of the end supply stopping, amazing explanation processors have emerged with custom architectures. Better speeds could also be achieved at competitive costs with the very useful ability of this custom hardware solution. In addition, there are many algorithms available and hardware-green that map the chips and that improve tempo and flexibility at the same time as complying with the desired signal processing obligations[1],[2] and[3]. An acronym for coordinate rotation of the digital PC, cordic with the useful resource Jack e Volder is one such reachable and hardware-efficient collection of hints [7].Cordic makes use of surely shift-and- add arithmetic with desk look-up to put in strain one of a kind functions. By way of making low priced adjustments to the preliminary stipulations and the lut values, it can additionally be used to effectually vicinity into have an impact on trigonometric, hyperbolic, exponential capabilities, coordinate adjustments and so forth. The utilization of the equal hardware. Because it makes use of absolutely shift-upload arithmetic, VLSIexecution of such an algorithm is besides trouble possible. DCT algorithm has particularly a quantity of knowledge and is extraordinarily used for picture compression. Enforcing DCT the utilization of cordic algorithm reduces the large vary of computations in the route of processing, will make higher the accuracy of reconstruction of the image, and reduces the chip area of implementation of a processor developed for this motive. This reduces the handy electrical energy intake. FPGA offers the hardware environment whereby dedicated processors might also additionally be examined for their capability. They attribute a diffusion of high-pace operations that cannot be positioned out with the useful resource of an undemanding microprocessor. The vital accumulate that FPGAprovides is on-website online programmability. For that reason, it types the high-quality platform to function in effect and check the generic common basic overall performance of a dedicated processor designed the utilization of cordic set of pointers [5].

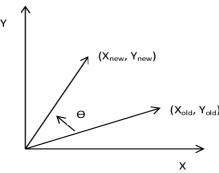

Fig. 1 Rotation of a vector by an angle in 2D circular coordinate system

$X_{new} = K (X_{old} Cos\theta - Y_{old} Sin\theta)$

$Y_{new} = K (X_{old} Sin\theta + Y_{old} Cos\theta)$

$R = K(X_{old}^2 + Y_{old}^2)^{05}$

$$\theta = \tan^{-1}(Y_{old}/X_{old})$$

The above conventional of equations may additionally be utilized in evaluating the coordinates of the vector(xnew, ynew) from the vector( $X_{old}$ ,  $Y_{old}$ ) that is grew to emerge as spherical with the beneficent aid of  $\theta$  an state of mind of in a 2nd spherical coordinate device. This is examined in the parent.

$$V_{new} = R V_{old}$$

$$V_{new} = \begin{bmatrix} Xnew \\ Ynew \end{bmatrix}$$

$$R = \begin{bmatrix} Cos\theta & -Sin\theta \\ Sin\theta & Cos\theta \end{bmatrix}$$

$$V_{old} = \begin{bmatrix} Xold \\ Yold \end{bmatrix}$$

$$R = KR_{p}$$

Where  $K = Cos\theta$

$$p = K. \begin{bmatrix} 1 & -tan\theta \\ 1 & tan\theta \end{bmatrix}$$

R

#### 2. Literature Review

For its navigational features, Cordic first was carried through jack e volder in 1959. The added cordic was once important to compare the trigonometric identities involved in the rotation and the transition of aircraft coordinates between polar and rectangular coordinates[1]. Subsequently, In order to evaluate some basic elements based fully on rounded, linear, and hyperbolic structures, in 1947, I. S. Walther unified the cordic that Volder had brought forward [2]. The cordic structure required several changes over the course of the fifty-four year period, and several iterations of the proposed rules at the beginning were established [3],[4]. Architectures combined with scaling-free cordic pipelines with low-latency mixed-scale rotations (MSR), have taken into account impressive deal use in contemporary digital systems [5] to [11]. Frequency synthesizers are a critical unit of many verbal communication systems, also called oscillators. Digital sub-structures use the complexity of digital systems to allow the use of digital structures increasingly widespread. With the introduction of digital systems. Direct Digital Synthesizers are categorized into the digital domain as frequency synthesizers that create preferred frequency waveforms [14]. These waveforms, including the sine, cosine, triangular, rectangular or rectangular, noteworthy tooth etc. are often referred to as the numerically controlled oscillators (NCO). There are broad uses in satellite television for PC communication systems, RF sign processing, etc. As described above. There is a lack of a DDS scheme for various verbal exogenous structures requiring quadrature inputs, e.g. every sin and cosine, for this reason. DDS has many advantages over analogue oscillators, including extremely precise decision to turn frequency, quick segment hoping, reduction of associated segment errors, remotely controllable, greater fitness of square outputs where appropriate, and so on. The DDS section to the amplification block specifies the quality of the synthesizer output. In the proposed format the construction of such a block is mainly based on pipeline CORDIC and hence produces square outputs as it is capable of generating each sinus and cosine wave at a time. Additionally, the section to conversion blocks in designing DDS is supported with other techniques such as the presence of the desk approach. The COR DIC mode applied to the amplitude block in the DDS graph is rotational mode and the gadget used for the coordinate is a round coordinate scheme. The CORDIC pipeline diagram enables a reduction in latency and increases the design speed. Due to the increased speed of operation and the various outputs for each clock cycle, the CORDIC pipeline has[2] benefit over a separate, totally committed architectural CORDIC (FDA). The stage of pipeline generation is identical to the one in FDA without registries are used to control the both input and output values of the pipeline CORDIC.

## 3. Research Issue & Future Scope

Accordingly, we can be aware of that cordic is one of the maximum identifying arithmetic strategies that has located some distance-achieving capabilities in digital systems. Area surroundings great and energy environment quality homes are constantly the favored wish of any dressmaker. As CORDIC buildings are truly built in every field, productivity and power productivity, architectures can be certainly designed to develop digital buildings based on CORDIC structures. The issues which are discussed are the evaluation of the limited data-width CORDIC unit (up to sixteen bits and every now and then two dozen bits), and to improve CORDIC's scale-free mapping mechanism to map the attitude to 360 °, an 8-point DFT core FPGA-compatible format, a direct digital synthesizer (DDS) FPGA plan and a plug-in tube FPGA System. The issue also answers the appeal. Unique DDS and FFT core integrated circuit (ASIC) format.

Scaling-free CORDIC Consequently, the above-mentioned architectures for the development of scale-free CORDIC usually have mass overhead hardware in contrast to conventional CORDIC, enabling designers to pay interest to create smaller or similar hardware overhead designs than standard CORDIC. Although latency is a different problem with these designs, the latency of pipelines to completely integrate architectures is constantly increased.

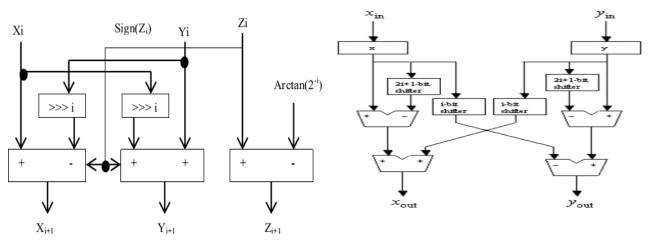

Fig3.1 Represent ithnumber repetition

Fig3.2 Relationship between i and bits

## Latency Scaling CORDIC

Within the DFT and FFTarchitectures, the use of CORDIC is preferred because it balances multiplier structures. There was a lot of work done. The problem with them is that each butterfly unit needs to be computed with a CORDIC unit. Very far less types of CORDIC gadgets than the prototypes [12] and [13] have been included in the proposed table. For CORDIC [14],[15] several architectural designs have been advanced. One of them is described in [17] and has a low latency, as opposed to the only one in [16].In keeping with this in mind, for revolution mode, after the CORDIC new release i = n/2, the place n is the complete huge form of bits inside the resultant vector, the x and y organizes ( $X_{n/2+1}$  and  $Y_{n/2+1}$ ) are turned around with the aid of the final attitude,  $W_{n/2+1}$ , as follows:

$$X_{f} = K_{N/2+1}(X_{N/2+1} + Y_{N/2+1}W_{N/2+1})$$

$$Y_{f} = K_{N/2+1}(Y_{N/2+1} - X_{N/2+1}W_{N/2+1})$$

The multiplication by w can be done with a logarithmic delay using a counter tree. Only after a linear approach to rotation is the constant multiplication done.

### 4. Proposed Methodology

The daily group fee is 0. 6173, the potential cost and values correctly deviate from the payment referred to and the variance is one-of-a-kind for top level inputs. Desk displays the congregation issue scale values for extraordinary input ranges. The DFT core used in its rotation mode is the CORDIC unit because the necessary expression using CORDIC is the same for the form  $XCos\Theta$  or  $XSin\Theta$ . As shown below, the concept is divided into actual and imaginary parts:

$$X[k] = \sum_{k=0}^{N-1} x[n] \cos(\frac{2\pi nk}{N}) - i \sum_{k=0}^{N-1} x[n] \sin(\frac{2\pi nk}{N})$$

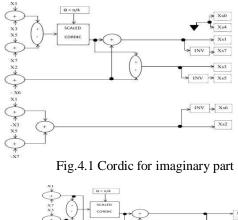

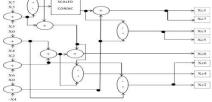

Two computer units, both for real terms and for complex terms, are constructed by exploring symmetry in addition and using DFT symmetry properties. Figure4.1 shows the proposed architecture that calculates fictional, sinic and related coefficients, Figure4.2 shows the architecture that calculates real, cosine-containing, coefficients. A scaled CORDIC system is used in both situations. It is obvious from the architecture that, for the calculation of sinusoidal terms, one CORDIC unit, and 9 adder / sub tractors, plus three INVs, are needed that deny the numbers on the basis of 2 supplementary logic. In rotating mode, the CORDIC unit is used.

Table 4.1Comparison of Output and Input Bits

| $X_{in} = Y_{in}$ | X <sub>out</sub> | Yout  | Scale<br>factor x | Scale<br>factor y |

|-------------------|------------------|-------|-------------------|-------------------|

| 14                | 23               | 25    | 0.6250            | 0.6035            |

| 60                | 99               | 102   | 0.5117            | 0.6037            |

| 511               | 758              | 846   | 0.5990            | 0.6040            |

| 3998              | 6410             | 6786  | 0.6158            | 0.6055            |

| 15841             | 25773            | 26189 | 0.6349            | 0.6066            |

## 5. Simulation Analysis

Xilinx ISE version 14 is used to test the proposed design. The FPGA mapping system used is XC2VP30. Verilog is the Hardware description Language (HDL) used to define the behavior of the device. The signed 2 supplement number system displays both inputs and outputs. Breakthrough of the data route. The input vector representation is known as both an integer and a fixed-point demonstration. As the data path width is specified, the selection of inputs should be carefully selected. This implies that during arithmetic operations no overflow can take place.

## 6. Conclusion

As consistent with current innovation future is in reality hooked up on a new redundant online CORDIC with regular scaling element was brought the utilization of the 2-D householder CORDIC. In comparison to in advance proposed procedures, our technique does no longer require difficult scaling problem calculation or greater correcting iterations, and may perform every and each CORDIC critiques (for state of mind calculation) and CORDIC capabilities (for rotation) if the calculation of the factor of view vicinity is protected. VLSI

implementation of the processor the utilization of modern-day photo structure technique is similarly given. We also suggested the implementation of DFT in a complex hardware architecture utilizing low-latency CORDIC. The number of adds/ subtractions has been reduced by exploring the transformation symmetry functionality, so that minimum power releases, limited area and better latencies are achieved. The proposed design was introduced by Xilinx FPGA developed with 0.13µm technology. In the proposed design very few exclusive multipliers (0 for DFTs with 8 points) and fewer adders were included than other traditional methods.

# References

- 1. Barozzi, Sara, et al. "Filtering images extracted from social media in the response phase of emergency events." 16th Conference on Information Systems for Crisis Response and Management. 2019.

- 2. Parmar, Yashrajsinh, and K. Sridharan. "A Resource-Efficient Multiplierless Systolic Array Architecture for Convolutions in Deep Networks." IEEE Transactions on Circuits and Systems II: Express Briefs 2019

- 3. Gurantz, Itzhak, Yoav Goldenberg, and Sree A. Raghavan. "Demodulator for consumer uses." U.S. Patent No.5, Aug. 1996, pp.550, 869.

- 4. Wang, Sicong, Zhiping Wen, and Lixin Yu. "High-performance fault-tolerant CORDIC processor for space usage." 2006 1st International Symposium on Systems and Control in Aerospace and Astronautics. IEEE, 2006.

- 5. Huang, Yi, Zhi-Qian Yang, and Li-Jun Guo. "Usage of CORDIC algorithm in processing of tethered pose of aerostat radar [J]." Journal of Hefei University of Technology (Natural Science) 11 (2010).

- 6. Hore, Alain, and Djemel Ziou. "Image quality metrics: PSNR vs. SSIM."TwentiethInternational Conference on Pattern Recognition. IEEE, 2010.

- 7. Zhang, Lin, Lei Zhang, and Xuanqin Mou. "RFSIM: A feature based image quality assessment metric using Riesz transforms." International Conference on Image Processing. IEEE, 2010.

- 8. Zhang, Lin, et al. "FSIM: A feature similarity index for image quality assessment." IEEE transactions on Image ProcessingAug. 20111pp. 2378-2386.

- 9. J.E. Volder,"The CORDIC Trigonometric Computing Technique" IRE Trans. Electron. Computers," vol. EC-8, Sept 1959, pp. 330- 334.

- J. S.Walther, "A unified algorithm for elementary functions," Spring Joint Computer Conf., 1971, pp. 379-385.

- 11. S. F. Hsiao, Y. H. Hu and T. B. Juang, "A Memory Efficient and High SpeedSine/Cosine Generator Based on Parallel CORDIC Rotations," IEEE Signal Pro-cessing Letters, vol. 11, No.2, Feb-2004, pp. 152-155.

- 12. Aarti Ranji, Nashrah Fatima, Paresh Rawat "Area efficient VLSI architecture for DCT using modified CORDIC algorithm" International Conference on Emerging Technological Trends 2016.

- 13. N Prasad, Ayas Kanta Swain, K. K. Mahapatra "Design and error analysis of a scale free CORDIC unit with corrected scale factor" Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics, 2012.

- 14. Abhishek Mankar, N Prasad, Ansuman DiptiSankar Das, Sukadev Meher. " Multiplierless VLSI architectures for radix-2 folded pipelined complex FFT core " International Journal of Circuit Theory and Applications, 2015.

- 15. Baozhou Zhu, Yuanwu Lei, Yuanxi Peng, Tingting He. "Low Latency and Low Error Floating-Point Sine/Cosine Function Based TCORDIC Algorithm" IEEE Transactions on Circuits and Systems I: Regular Papers, 2017.

- 16. N. Takagi, T. Asada, and S. Yajima, "Redundant CORDIC methods with a constantscale factor for sine and cosine computation," IEEE Trans. Computers, vol. 40,Sept 1991, pp.989-995.

- 17. K. Maharatna and S. Banerjee, "A VLSI array architecture for hough transform," Pattern Recognit., vol. 34, 2001,pp. 1503-1512.

- 18. K. Maharatna, A. S. Dhar, and S. Banerjee, "A VLSI array architecture for realization of DFT, DHT, DCT and DST," Signal Process., vol. 81, 3- 1822.

- 19. Y.H. Hu and H. M.Chern, "VLSI CORDIC array structure implementation of Toeplitz eigensystem solvers," in Proc. IEEE Int. Conf. Acoust. Speech, Signal Processing, NM, 1990, pp. 1575-1578..

- Pramod K. Meher, Javier Walls, Tso-Bing Juang, K. Sridharan, Koushik Ma- haratna, "50 Years of CORDIC: Algorithms, Architectures and Usage," IEEE Transactions on Circuits and Systems-I: Regular Papers, Vol. 56, No.9, Sept.2009,pp. 1893- 1907.

- 21. C. S. Wu and A. Y. Wu, "Modified vector rotational CORDIC (MVR-CORDIC) algorithm and architecture," IEEE Trans. Circuits Syst.II, vol.48,June 2001 pp. 548-561.

- 22. Cheng-Shing Wu, An-Yeu Wu and Chih-Hsiu Lin,"A High- Performance/Low- Latency Vector Rotational CORDIC Architecture Based on Extended Elementary Angle Set and Trellis-Based Searching Schemes," IEEE Transcations on Circuits and SystemsII : Analog and Digital Signal Processing, Vol.50,No.9, Sept. 2003,pp.589-601.

- 23. Y. H. Hu and S. Naganathan, An angle recoding method for CORDIC algorithm implementation, IEEE Trans. Computers, vol. 42, Jan. 1993, pp. 99–102.

- 24. K. Maharatna, S. Banerjee, E. Grass, M. Krstic, and A. Troya, Modified virtually scaling-free adaptive CORDIC rotator algorithm and architecture, IEEE Trans. Circuits Syst. Video Technol., vol. 15, no. 11, Nov. 2005, pp. 1463-1474.

- 25. K.Maharatna, A.Troya, S.Banerjee, and E. Grass, "Virtually scaling free adaptive CORDIC rotator," IEE Proc.-Comp. Dig. Tech., vol.-151, no.6, Nov.2004, pp. 448- 456.

- 26. Leena Vachhani, K. Sridharan and Pramod K. Meher, "Efficient CORDIC Algorithms and Architectures for Low Area and High Throughput Implementation," IEEE Transactions on Circuit and Systems-II,vol. 56, No. 1, January 2009, pp.61-65.

- 27. F.J. Jaime, M. A. Sanchez, J. Hormigo, J.Villalba and E. L. Zapata, "Enhanced scaling-free CORDIC," IEEE Trans. Circuits and Systems-I: Regular Papers, vol.57,No.7, July 2010pp. 1654-1662.

- Supriya Aggarwal, P.K Meher and K. Khare "Area-Time Efficient Scaling-Free CORDIC Using Generalized Micro-Rotation Selection," IEEE Transactions on Very LargeScaleIntegration(VLSI)Systems, Vol.20, No.8, August2012, pp. 1542-1546.

- 29. MatteoCauso, Ting an and Alves de Barros Naviner "Parallel scaling-free and area-time efficient CORDIC Algorithm," 19th IEEE International Conference on Electronics, Circuits and Systems, 2012, pp.149-152.

- 30. Supriya Aggarwal, K. Khare, "Hardware Efficient Architecture for Generating Sine/Cosine Waves,"25th International Conference on VLSI Design 2012.

- 31. S. Aggarwal, P.K Meher and K. Khare, "Scale-Free Hyperbolic CORDIC Processor and Its Usage to Waveform Generation," IEEE Transactions on Circuits and Systems-I, vol.60, No.2, 2013, pp.314-326

- 32. J. Vankka, "Digital Synthesizers and Transmitters for Software Radio," Dordrecht, Netherlands. Springer: 2005.

- 33. Maher Jridi and Ayman Alfalou. "Direct Digital Frequency Synthesizer with CORDIC Algorithm and Taylor Series Approximation for Digital Receivers," European Journal of Scientific Research, Euro Journals, vol 30 (4), 2009, pp.542-553.

- 34. Nitesh Kumar Sharma, Dr. Shanti Rathore and Dr. M.R. Khan "A Comparative Analysis on Coordinate Rotation Digital Computer (CORDIC) Algorithm and Its use on Computer Vision Technology," First International Conference on Power, Control and Computing Technologies, 2020, pp., 106-110.

- 35. Nitesh Kumar Sharma, Shanti Rathore and M.R. Khan "CV(Computer Vision) System By Cordic Processing Unit" Jourbal Of Critical Reviews Vol.7(18),2020, pp.2235-2241.