# Three-Phase Symmetrical Multilevel Converter for Grid-Connected PV Systems: Enhancing Power Quality and Efficiency in Distributed Generation

G. Ismayel<sup>1</sup>, T. Bhavani<sup>1</sup>, K. Shankar<sup>1</sup>

<sup>1</sup>Assistant Professor, Dept. of EEE, Malla Reddy Engineering College and Management Sciences, Medchal, Hyderabad, India

# **ABSTRACT**

In this paper, we present a new three-phase symmetrical multilevel converter for grid-connected systems using a PV source. Renewable energy sources are the application of distributed generation (DG) in the distribution system and have gained more attention. The distribution generation systems are powered by microsources such as fuel cells, photovoltaic (PV) systems, and batteries. PV-distributed system in which the solar source is low-dc input voltage interfaced to the grid using front-end conversion. Three-phase Cascaded H-Bridge A seven-level inverter is interfaced with a low-frequency transformer with multiple PV sources. Nowadays, multilevel inverters (MLI) play a vital role in the field of power electronics and are widely used in many industrial and commercial applications. Moreover, advantages like high-quality power output, low switching losses, low electro-magnetic interference (EMI), and high output voltage make multilevel inverters a powerful solution in converter topology.

**Keywords:** Multilevel Inverter, PV panel, Distributed generation, and MATLAB.

### I. INTRODUCTION

Recently, multi-level inverters great attention as a single stage inverter. Although, they have obtained need high number of components, but due to their advantages such as generating output voltage with extremely low distortion factor, low dv/dt, small output filter size, low electromagnetic interface, and low total harmonic distortion, still have great attention. Practically, all of these advantages appear strongly as the number of dc-power sources increased as in the case of renewable energy systems. The general concept of is to utilize isolated dc sources or a bank of series capacitors to produce ac voltage waveforms with higher amplitude and near sinusoidal waveform. There are three conventional types of named as neutral point diode clamped, flying capacitor, and cascaded H-Bridge. Almost all of them are suffering from increased components number per level, and complex control architecture.

Among the different topologies for, they can be classified into two main categories: 1) single dcsource inverter such as, and inverters; 2) multi-dc sources inverters such as inverter. While, multi-dc sources inverter is divided into symmetrical and no symmetrical topologies. principally, symmetrical topologies produce more voltage levels compared to symmetrical topologies. Almost all of these topologies can be extended for more voltage levels by increasing the number of the primary configuration (basic cell). Many topologies were presented in the last decade focusing on minimizing the basic multilevel topologies drawbacks. The author in presented a topology named multilevel dc link. It consists of a group of

basic cells connected in series configuration. Each cell produces or 0 voltage across the connected cells, there is an H-bridge to change the polarity of the synthesized voltage. The required number of active switches for output voltage levels is for the inverters. However, this topology requires increased number of components compared to the conventional topologies, and high voltage stresses.

However, in the authors presented a topology named transistor-clamped H-bridge. The primary cell can produce five-levels per pole in the output voltage. However, it suffers also from the increased components counts, requirements of electrolytic capacitors, complex control methodology

# II. PHOTOVOLTAIC MODULE

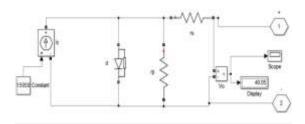

Modelling is the basis for computer simulation of a real system. It is usually based on a theoretical analysis of the various physical processes occurring in the system and of all factors influencing these processes. The most common model used to predict energy production in photovoltaic cell modelling is the single diode circuit model that represents the electrical behaviour of the pn-junction is given in fig 1.

Figure 1: Single diode model of a solar cell.

Figure shows how photovoltaic system works. The ideal photovoltaic module consists of a single diode. A solar cell is the building block of a solar panel. A photovoltaic module is formed by connecting many solar cells in series and parallel. Considering only a single solar cell; it can be modelled by utilizing a current source, a diode and two resistors. This model is known as a single diode model of solar cell.

# III. PROPOSED MODULAR MLI

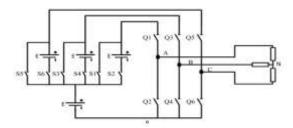

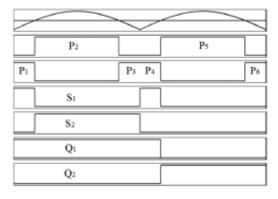

new modular three-phase with reduced components count is proposed and studied in this paper. The suggested three phase symmetrical inverter is shown in Fig 2(a). Each arm consists of series connection of basic cells with a series connected switch, for example arm A is consists of one cell connected in series with switch. Adding the common dc voltage source in to each arm forms the pole, creating the pole voltages. In order to obtain the zero state pole voltage another switch is added to the pole, similarly and for pole and.

Fig 2(a) Proposed three-phase MLI topology.

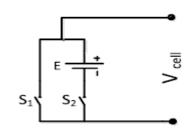

Fig 2(b) Basic cell

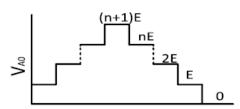

Fig 2(c) Pole voltage waveform for n-ce

Fig 2(b) shows the primary basic cell, where each cell consists of two switches and single dc voltage source. The two switches operate in a complementary fashion. Therefore, each cell can produce two voltage levels: when in ON-STATE, zero voltage is produced across the cell terminals,

and when in ON-STATE, volt is applied across the cell terminals. Furthermore, using only one cell per each pole and applying suitable control signals to the, and, three voltage levels per pole are produced. The output pole voltage for cells connected in series configuration is shown in Fig 2(c). The proposed topology is a modular type therefore it can be extended to any levels. Equations (1)–(4) provide the relations of the proposed topology as

$$N_{Pole} = N_{Cell} + 2 \tag{1}$$

$$M_{Level} = 2N_{Cell} + 3 \tag{2}$$

$$N_{SW} = 3(2N_{Cell} + 2) \tag{3}$$

$$N_{PS} = 3N_{Cell} + 1 \tag{4}$$

Then for the example of, [based on (2)] which is the pole voltage levels and [based on (3)] which is the output line-to-line voltage levels. Note that the number of output phase voltage levels will be derived to be seven levels in low frequency modulation and nine levels for high frequency modulation.

# IV. MODULATION TECHNIQUES FOR THE PROPOSED MLI

# A. Low Frequency Modulation Technique

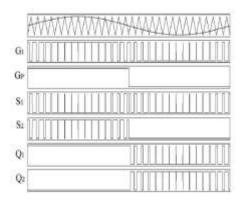

The low frequency modulation is considered as the basic modulation technique due to its lower switching frequency than the other modulation methods. It causes the switching loses reduced dramatically. In order to investigate the performance of the proposed, three levels per pole by using single basic cell in each pole is used as shown in Fig 2. It is simulated via PSIM and MATLAB/SIMULINK software packages. In order to generate the required switching signals for the proposed, a rectified sine waveform has a frequency equal to the output voltage frequency (50 Hz) is compared with a dc voltage signal has an amplitude equal to half of the sine wave amplitude as shown in Fig. 3.

Fig. 3 Switching patterns for low frequency modulation technique

Research Article

The intersection points between them identify six periods. Four switching signals are constructed from these periods combination in order to generate a sinusoidal output voltage. The control equations for the  $(S_1, S_2, S_3 \text{ and} S_4)$  are given in (5)–(9), respectively. The same scenario is applied to inverter poles and after shifting the basic sinusoidal voltage with -120 $^0$ , 120 $^0$ , respectively.

Therefore, the required switching signals for the overall three poles can be generated

$$S_1 = P_1 + P_4 \tag{5}$$

$$S_2 = P_2 + P_3 \tag{6}$$

$$Q_1 = P_1 + P_2 + P_3 + P_4 \tag{7}$$

$$Q_2 = P_5 + P_6 (8)$$

B. Sinusoidal Pulse-Width Modulation Technique (SPWM):

The straight way to generate the *SPWM* signals is to compare a sinusoidal waveform signal with a triangular waveform. The comparison operation will produce the Boolean signals that are required to synthesize the switches control pulses. The *SPWM* technique is successfully applied for the proposed topology. Two different approaches have been proposed as follows.

1) Scheme I: SPWM Using Single Carrier Signal: This scheme uses one carrier signal centered with the sinusoidal modulation signal (sine waveform), and it has an amplitude equal to peak-to-peak value of the modulation signals as shown in Fig. 4.

Fig. 4 Switching patterns of the proposed MLI for scheme I.

It worth mentioning that the modulation signal is shifted by dc level equals to (CR/2), where CR is the carrier signal amplitude. The resulted Boolean output from the comparison between the carrier and the modulating signal produces the main pulse signal  $G_1$ . Also the pulse signal  $GP_1$  is generated by comparing the modulating signal with zero value. After logical processing on  $G_1$  and  $GP_1$ , the switching pulses  $S_1$ ,  $S_2$ ,  $Q_1$ , and  $Q_2$  can be generated as specified in (9)–(12).

$$S_1 = (G_1 X \overline{GP_1}) + (\overline{G_1} X GP_1) \tag{9}$$

$$S_2 = (G_1 \ X \ GP_1) \tag{10}$$

$$Q_1 = GP_1 + \{ (G_1 X \overline{GP_1}) + (\overline{G_1} X GP_1) \}$$

(11)

$$Q_2 = \overline{\left\{ \overline{GP_1} \ X \ \overline{\left(G_1 \ X \ \overline{GP_1}\right)} \right\}} \tag{12}$$

Where stands for logic AND, stands for logic OR stands for invert, and are the signals which will be applied to the gates drive belongs to switches respectively. In order to avoid dc-power sources short circuit operate in a complementary mode with dead time.

2) Scheme II: SPWM Using Two Carrier Signals: This scheme compares single modulating signal with two identical and shifted in level carrier signals. Both of them have amplitude equal the modulating signal peak. In addition, the carrier signals are shifted by a dc offset equals to the carrier signal amplitude as shown in Fig. 5.

Fig. 5 Switching patterns of the proposed MLI for scheme II

Using the same procedure followed in scheme I, scheme II can be executed. However, due to using two carrier signals, there are two Boolean signals named and resulted from the comparison. By Carrying out several logical operations on these two signals as given in (13)–(16), the required control pulses for can be obtained

$$S_1 = (G_1 X \overline{G_2}) \tag{13}$$

$$S_2 = G_2 \tag{14}$$

$$Q_1 = \overline{\overline{G_2} \, X \, \overline{(G_1 \, X \, \overline{G_2})}} \tag{15}$$

$$Q_2 = \overline{G_2} X \overline{(G_1 X \overline{G_2})}$$

(16)

#### V. SIMULATION RESULTS

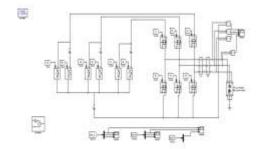

Fig. 6: Simulink model of proposed system.

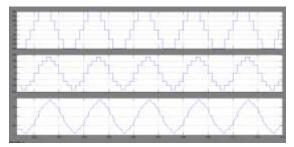

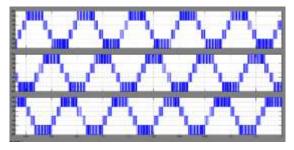

Fig. 7 line to line, phase voltages and phase current with low frequency modulation

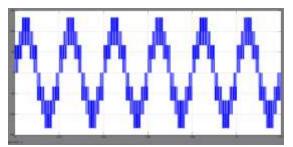

Fig. 8 line to line voltages with SPWM modulation technique

Fig. 9 phase voltages with SPWM modulation technique

### VI. CONCLUSION

To have sustainable growth and social progress, it is necessary to meet the energy need by utilizing the renewable energy resources like wind, biomass, hydro, co-generation, etc. In sustainable energy system, energy conservation and the use of renewable source are the key paradigm. So, these new technologies of semiconductor are more suited to high power applications and they enable the design of multilevel inverters. Compared to typical PWM switching schemes, multilevel fundamental switching will lead to lower switching losses. As a result, using the multilevel fundamental frequency switching scheme will lead to increased efficiency.

# **REFERENCES**

- [1] S. J. Park, F. S. Kang, M. H. Lee, and C. U. Kim, "A new single-phase five-level PWM inverter employing a deadbeat control scheme," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 831–843, May 2003.

- [2] V. G. Agelidis, D. M. Baker, W. B. Lawrance, and C. V. Nayar, "A multilevel PWM inverter topology for photovoltaic applications," in *Proc. Int. Symp. Ind. Electron.*, Jul. 1997, vol. 2, pp. 589–594.

- [3] G. J. Su, "Multilevel DC-link inverter," *IEEE Trans. Ind. Appl.*, vol.41, no. 3, pp. 848–854, May–Jun. 2005.

- [4] M. Calais, L. J. Borle, and V. G. Agelidis, "Analysis of multicarrier PWM methods for a single-phase five level inverter," in *Proc. Power Electron. Specialists Conf.*, 2001, vol. 3, pp. 1351–1356.

- [5] C. T. Pan, C. M. Lai, and Y. L. Juan, "Output current ripple-free PWMinverters," *IEEE Trans. Circuits Syst. II, Exp. Briefs.*, vol. 57, no. 10,pp. 823–827, Oct. 2010.

- [6] T. C. Neugebauer, D. J. Perreault, J. H. Lang, and C. Livermore, "Asix-phase multilevel inverter for MEMS electrostatic induction micro motors, "*IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 51, no. 2, pp.49–56, Feb. 2004.

- [7] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523,Sep. 1981.

- [8] M. F. Escalante, J. C. Vannier, and A. Arzandé, "Flying capacitor multilevel inverters and DTC motor drive applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 809–815, Aug. 2002.

- [9] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

- [10] M. A. Pérez, S. Bernet, J. Rodriguez, S. Kouro, and R. Lizana, "Circuit topologies, modeling, control schemes, and applications of modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 30, no. 1,pp. 4–17, Jan. 2015.