# A New Architecture: An Application of Fixed and Reconfigurable FIR Filter

# Ramya Sree B<sup>1</sup>, Prasanna A<sup>1</sup>, Ramesh L<sup>1</sup>

<sup>1</sup>Department of ECE, Sree Dattha Institute of Engineering and Science, Hyderabad, Telangana, India.

#### Abstract

Transpose form finite-impulse response (FIR) channels are inalienably pipelined and bolster multiple constant multiplications (MCM) system that outcomes in noteworthy sparing of calculation. Notwithstanding, transpose shape setup does not specifically bolster the piece handling dissimilar to direct form design. In this paper, we investigate the likelihood of acknowledgment of piece FIR channel in transpose frame design for territory defer effective acknowledgment of expansive request FIR channels for both settled and reconfigurable applications. In view of a point by point computational examination of transpose frame design of FIR channel, we have determined a stream chart for transpose shape piece FIR channel with enhanced enroll multifaceted nature. A summed-up piece plan is introduced for transpose shape FIR channel. We have determined a general multiplier-based design for the proposed transpose frame square channel for reconfigurable applications. A low-multifaceted nature configuration utilizing the MCM plot is likewise exhibited for the piece usage of settled FIR channels. The proposed structure includes altogether less area delay product (ADP) and energy per sample (EPS) than the current piece execution of direct-frame structure for medium or vast channel lengths, while for the short-length channels, the square usage of direct-shape FIR structure has less ADP and less EPS than the proposed structure.

# 1. Introduction

Finite impulseresponse (FIR) advanced channel is generally utilized as a part of a few advanced flag preparing applications, such as discourse preparing, boisterous speaker evening out, resound cancelation, versatile clamor cancelation, and different correspondence applications, including programming characterized radio (SDR) thus [1]. A large portion of these applications require FIR channels of extensive request to meet the stringent recurrence determinations [2-4]. All the time these channels need to help high examining rate for fast computerized correspondence [5]. The quantity of duplications and increases required for each channel yield, nonetheless, increments directly with the channel arrange. Since there is no excess calculation accessible in the FIR channel calculation, ongoing usage of a substantial request FIR channel in a asset obliged condition is a testing assignment. Channel coefficients all the time stay consistent and known from the earlier in flag preparing applications. This element has been used to diminish the multifaceted nature of acknowledgment of increases. A few outlines have been recommended by different analysts for productive acknowledgment of FIR channels (having settled coefficients) utilizing conveyed distributed-arithmetic (DA) [6] and multiple constant multiplication (MCM) techniques [7-10]. DA-based outlines look up tables (LUTs) to store precomputed results to diminish the computational many-sided quality.

The MCM strategy then again lessens the number of increments required for the acknowledgment of duplications by regular subexpression sharing, when a given info is duplicated with an arrangement of constants. The MCM plot is more viable, when a typical operand is increased with additional number of constants. In this manner, the MCM plot is appropriate for the execution of huge request FIR channels with settled coefficients. Be that as it may, MCM squares can be shaped just in the transpose frame design of FIR channels. Piece handling technique is famously used to infer high-

throughput equipment structures. It not just gives throughput-adaptable plan additionally enhances the region delay proficiency. The determination of square based FIR structure is clear when coordinate frame setup is utilized, though the transpose shape arrangement does not specifically bolster square preparing. Be that as it may, to take the computational favorable position of the MCM, FIR channel is required to be figured it out by transpose shape setup. Aside from that, transpose frame structures are inalienably pipelined and expected to offer higher working recurrence to help higher testing rate.

#### 2. Computational Analysis and Mathematical Formulation of Block Transpose Form Fir Filter

The output of FIR filter of length N can be computed using the relation

$$y(n) = \sum_{i=0}^{N-1} h(i) \cdot x(n-i).$$

The computation of (1) can be expressed by the recurrence relation

$$Y(z) = [z^{-1}(\cdots(z^{-1}(z^{-1}h(N-1) + h(N-2)) + h(N-3))$$

$$\cdots + h(1)) + h(0)]X(z).$$

#### 2.1. Computational Analysis

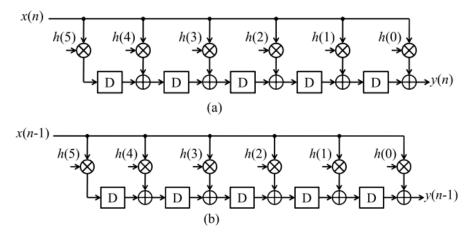

The data-flow graphs (DFG-1 and DFG-2) of transpose formFIR filter for filter length N = 6, as shown in Fig. 1, for a square of two progressive yields  $\{y(n), y(n - 1)\}$  that are gotten from. The item esteems and their aggregation ways in DFG-1 and DFG-2 of Fig. 1 are appeared in dataflow tables (DFT-1 and DFT-2) of Fig. 2. The bolts in DFT-1 and DFT-2 of Fig. 2 speak to the collection way of the products. We locate that five estimations of every section of DFT-1 are same as those of DFT-2 (appeared in dark shading in Fig. 2).

Figure 1. DFG of transpose form structure for N = 6. (a) DFG-1 foroutput y(n). (b) DFG-2 for output y(n - 1).

These repetitive calculation of DFG-1 and DFG-2 can be abstained from utilizing nonoverlapped succession of info obstructs, as appeared in Fig. 3. DFT-3 and DFT-4 of DFG-1 and DFG-2 for nonoverlapping input squares are, separately, appeared in Fig. 3(a) and (b). As appeared in Fig. 3(a) and (b), DFT-3 what's more, DFT-4 don't include excess calculation. It is simple to find that the sections in dark cells in DFT-3 and DFT-4 of Fig. 3(a) and (b) compare to the yield y(n), while the different sections of DFT-3 and DFT-4 relate to y(n–1). The DFG of Fig. 1 should be changed fittingly to acquire the calculations as per DFT-3 and DFT-4.

| ccs | M <sub>1</sub> | M <sub>2</sub>                       | M <sub>3</sub> | $M_4$      | M <sub>5</sub> | M <sub>6</sub> |

|-----|----------------|--------------------------------------|----------------|------------|----------------|----------------|

| 1   | x(n-5)h(5)     | <i>x</i> ( <i>n</i> -5) <i>h</i> (4) | x(n-5)h(3)     | x(n-5)h(2) | x(n-5)h(1)     | x(n-5)h(0)     |

| 2   | x(n-4)h(5)     | $\mathbf{x}(n-4)h(4)$                | x(n-4)h(3)     | x(n-4)h(2) | x(n-4)h(1)     | x(n-4)h(0)     |

| 3   | x(n-3)h(5)     | $\mathbf{x}(n-3)h(4)$                | x(n-3)h(3)     | x(n-3)h(2) | x(n-3)h(1)     | x(n-3)h(0)     |

| 4   | x(n-2)h(5)     | $\mathbf{x}(n-2)h(4)$                | x(n-2)h(3)     | x(n-2)h(2) | x(n-2)h(1)     | x(n-2)h(0)     |

| 5   | x(n-1)h(5)     | x(n-1)h(4)                           | x(n-1)h(3)     | x(n-1)h(2) | x(n-1)h(1)     | x(n-1)h(0)     |

| 6   | x(n)h(5)       | $\mathbf{x}(n)h(4)$                  | x(n)h(3)       | x(n)h(2)   | x(n)h(1)       | x(n)h(0)       |

| ccs | M <sub>1</sub> | M <sub>2</sub> | M <sub>3</sub> | M4         | M <sub>5</sub> | M <sub>6</sub> |  |

|-----|----------------|----------------|----------------|------------|----------------|----------------|--|

| 1   | x(n-6)h(5)     | x(n-6)h(4)     | x(n-6)h(3)     | x(n-6)h(2) | x(n-6)h(1)     | x(n-6)h(0)     |  |

| 2   | x(n-5)h(5)     | x(n-5)h(4)     | x(n-5)h(3)     | x(n-5)h(2) | x(n-5)h(1)     | x(n-5)h(0)     |  |

| 3   | x(n-4)h(5)     | x(n-4)h(4)     | x(n-4)h(3)     | x(n-4)h(2) | x(n-4)h(1)     | x(n-4)h(0)     |  |

| 4   | x(n-3)h(5)     | x(n-3)h(4)     | x(n-3)h(3)     | x(n-3)h(2) | x(n-3)h(1)     | x(n-3)h(0)     |  |

| 5   | x(n-2)h(5)     | x(n-2)h(4)     | x(n-2)h(3)     | x(n-2)h(2) | x(n-2)h(1)     | x(n-2)h(0)     |  |

| 6   | x(n-1)h(5)     | x(n-1)h(4)     | x(n-1)h(3)     | x(n-1)h(2) | x(n-1)h(1)     | x(n-1)h(0)     |  |

| (b) |                |                |                |            |                |                |  |

1.5

Figure 2. (a) DFT of multipliers of DFG shown in Fig. 1(a) corresponding tooutput y(n). (b) DFT of multipliers of DFG shown in Fig. 1(b) corresponding to output y(n - 1). Arrow: accumulation path of the products.

| ccs         | M1                                      | M2                                      | M <sub>3</sub>                                        | M4                                      | M5                                      | M <sub>6</sub>                          |

|-------------|-----------------------------------------|-----------------------------------------|-------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| 1           | x(n-10)h(5)                             | x(n-10)h(4)                             | x(n-10)h(3)                                           | x(n-10)h(2)                             | x(n-10)h(1)                             | x(n-10)h(0)                             |

| 2           | x(n-8)h(5)                              | x(n-8)h(4)                              | x(n-8)h(3)                                            | x(n-8)h(2)                              | x(n-8)h(1)                              | x(n-8)h(0)                              |

| 3           | x(n-6)h(5)                              | x(n-6)h(4)                              | x(n-6)h(3)                                            | x(n-6)h(2)                              | x(n-6)h(1)                              | x(n-6)h(0)                              |

| 4           | x(n-4)h(5)                              | x(n-4)h(4)                              | x(n-4)h(3)                                            | x(n-4)h(2)                              | x(n-4)h(1)                              | x(n-4)h(0)                              |

| 5           | x(n-2)h(5)                              | x(n-2)h(4)                              | x(n-2)h(3)                                            | x(n-2)h(2)                              | x(n-2)h(1)                              | x(n-2)h(0)                              |

| 6           | x(n)h(5)                                | x(n)h(4)                                | x(n)h(3)                                              | x(n)h(2)                                | x(n)h(1)                                | x(n)h(0)                                |

|             |                                         |                                         |                                                       |                                         |                                         |                                         |

| cs          | M.                                      | Ma                                      | (a)<br>M2                                             | M.                                      | Mc                                      | Mc                                      |

| ecs<br>1    | M <sub>1</sub><br>x(n-11)h(5)           | M <sub>2</sub><br>x(n-11)h(4)           | (a)<br>M <sub>3</sub><br>x(n-11)h(3)                  | M <sub>4</sub><br>x(n-11)h(2)           | M <sub>5</sub><br>x(n-11)h(1)           | M <sub>6</sub><br>x(n-11)h(0)           |

| 2 ces       |                                         |                                         | M <sub>3</sub>                                        |                                         |                                         | 0                                       |

| 1           | x(n-11)h(5)                             | x(n-11)h(4)                             | M <sub>3</sub><br>x(n-11)h(3)                         | x(n-11)h(2)                             | x(n-11)h(1)                             | x(n-11)h(0)                             |

| 1           | x(n-11)h(5)<br>x(n-9)h(5)               | x(n-11)h(4)                             | $M_3$<br>x(n-11)h(3)<br>x(n-9)h(3)                    | x(n-11)h(2)<br>x(n-9)h(2)               | x(n-11)h(1)<br>x(n-9)h(1)               | x(n-11)h(0)<br>x(n-9)h(0)               |

| 1<br>2<br>3 | x(n-11)h(5)<br>x(n-9)h(5)<br>x(n-7)h(5) | x(n-11)h(4)<br>x(n-9)h(4)<br>x(n-7)h(4) | $\frac{M_3}{x(n-11)h(3)}$<br>x(n-9)h(3)<br>x(n-7)h(3) | x(n-11)h(2)<br>x(n-9)h(2)<br>x(n-7)h(2) | x(n-11)h(1)<br>x(n-9)h(1)<br>x(n-7)h(1) | x(n-11)h(0)<br>x(n-9)h(0)<br>x(n-7)h(0) |

Fig. 3. DFT of DFG-1 and DFG-2 for three nonoverlapped input blocks [x(n), x(n-1)], [x(n-2), x(n-3)], and [x(n-4), x(n-5)]. (a) DFT-3 for computation of output y(n). (b) DFT-4 for computation of output y(n-1).

# **3. Proposed Structures**

There are a few applications where the coefficients of FIR channels stay settled, while in some different applications, like SDR channelizer that requires isolate FIR channels of diverse details to remove one of the coveted narrowband channels from the wideband RF front end. These FIR channels should be actualized in a RFIR structure to help multistandard remote correspondence. In this segment, we exhibit a structure of piece FIR channel for such reconfigurable applications. In this segment, we talk about the execution of piece FIR channel for settled channels also utilizing MCM plot.

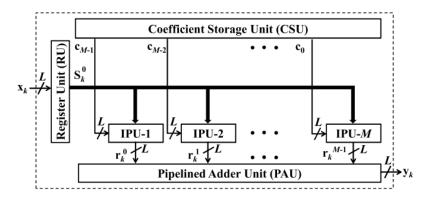

#### 3.1. Transpose Form Block FIR Filter for Reconfigurable Applications

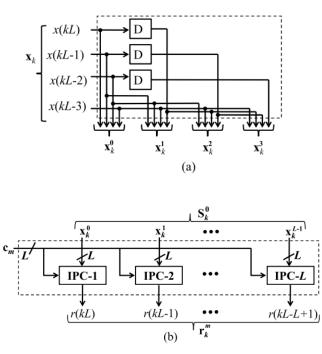

The proposed structure for block FIR filter is shown in Fig. 4 for the block size L = 4. It consists of one coefficient selection unit (CSU), one register unit (RU), *M* number of inner product units (IPUs), and one pipeline adder unit (PAU). The CSU stores coefficients of the considerable number of channels to be utilized for the reconfigurable application. It is actualized utilizing *N* ROM LUTs, with the end goal that channel coefficients of a specific direct channel are acquired in one clock cycle, where N is the channel length. The RU [shown in Fig. 5(a)] gets  $x_k$  amid the  $k_{th}$  cycle and creates *L* lines of  $S_k^0$  in parallel. *L* columns of  $S_k^0$  are transmitted to *M* IPUs of the proposed structure. The *M* IPUs additionally get *M* short-weight vectors from the CSU with the end goal that amid the  $k_{th}$  cycle, the (m + 1)th IPU gets the weight vector  $c_M - m - 1$  from the CSU and *L* lines of  $S_k^0$  frame the RU. Each IPU performs lattice vector result of  $S_k^0$  with the short-weight vector  $c_m$  and figures a piece of *L* fractional channel yields  $r_k^m$ . Along these lines, each IPU performs *L* inward item calculations of *L* columns of  $S_k^0$  with a typical weight vector  $c_m$ . The structure of the (m+1)th IPU is appeared in Fig. 5(b).

Figure4. Proposed structure for block FIR filter.

Figure 5. (a) Internal structure of RU for block size L = 4. (b) Structure of (m + 1)th IPU.

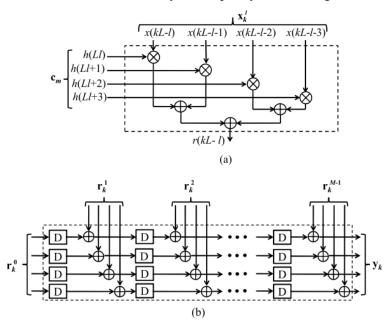

It comprises of *L* number of *L* -point inward item cells (IPCs). The (l + 1)th IPC gets the (l + 1)th column of  $S_k^0$  and the coefficient vector cm, and figures a halfway aftereffect of internal item r(kL - l), for  $0 \le l \le L - 1$ . Interior structure of (l + 1)th IPC for L = 4 is appeared in Fig. 6(a). All the M IPUs work in parallel and create *M* locks of result  $(r_k^m)$ . These incomplete internal items are included the PAU [shown in Fig. 6(b)] to get a square of L channel yields. In each cycle, the proposed structure gets a square of sources of info and produces a piece of L channel yields, where the term of each cycle is  $T = T_M + T_A + T_{FA} \log_2 L$ ,  $T_M$  is one multiplier delay,  $T_A$  is one adder delay, and  $T_{FA}$  is one full-adder delay.

#### 3.2. MCM-Based Implementation of Fixed-Coefficient FIR Filter

We talk about the deduction of MCM units for transpose shape piece FIR channel, and the plan of proposed structure for settled channels. For settled coefficient usage, the CSU of Fig. 6 is never again required, since the structure is to be custom-made for just a single given channel. Correspondingly, IPUs are not required. The increases are required to be mapped to the MCM units for a low-many-sided quality acknowledgment.

Figure 6. (a) Internal structure of (l + 1)th IPC for L = 4. (b) Structure of PAU for block size L = 4.

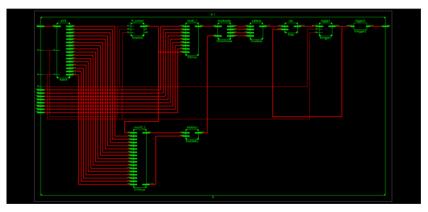

Figure 7. RTL schematic diagram

In the accompanying, we demonstrate that the proposed detailing for MCM-based execution of square FIR channel makes utilization of the symmetry in input grid S0k to perform even and vertical basic subexpression end [11] and to limit the quantity of move include operations in the MCM squares.

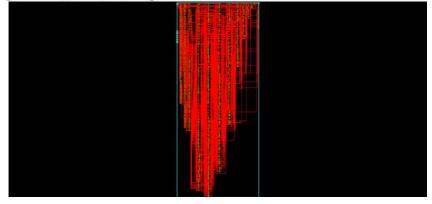

Figure 8. Technological schematic diagram

|             |                |                                         |                   |                        |                         | 1,000.000 ns        |

|-------------|----------------|-----------------------------------------|-------------------|------------------------|-------------------------|---------------------|

| Name        | Value          |                                         |                   |                        |                         | 1800 ns             |

| y(15:0)     | 01000011100000 | 000000000000000000000000000000000000000 | 0000100001 000100 | 0011X0001100101X001000 | 00111 0010101000 001100 | 1010X0011101100X010 |

| 16 cim      | 1              |                                         |                   |                        |                         |                     |

| 16 dk1      | 0              |                                         |                   |                        |                         |                     |

| 16 dk2      | 0              |                                         |                   |                        |                         |                     |

| ▶ 📷 ×[7:0]  | 10110000       | 00000000                                |                   | 10110                  | 000                     |                     |

| h0[7:0]     | 00000101       | 00000000                                | <                 | 00000                  | 101                     |                     |

| h1[7:0]     | 00100000       | 00000000                                | <                 | 00100                  | 000                     |                     |

| ▶ 🏹 h2[7:0] | 01000001       | 00000000                                |                   | 01000                  | 001                     |                     |

| 🕨 🏹 h3[7:0] | 00111000       | 00000000                                |                   | 00111                  | .000                    |                     |

| ▶ 📷 h4[7:0] | 00111000       | 00000000                                | <                 | 00111                  | .000                    |                     |

| ▶ 🏹 h5[7:0] | 00001000       | 00000000                                |                   | 00001                  | .000                    |                     |

| 🕨 📷 h6[7:0] | 00101101       | 00000000                                |                   | 00101                  | 101                     |                     |

| ▶ 📷 h7(7:0) | 01001100       | 00000000                                |                   | 01001                  | .100                    |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                |                                         |                   |                        |                         |                     |

|             |                | X1: 1,000.000 ns                        |                   |                        |                         |                     |

Figure 9. Simulation outcome

# 4. Conclusion

In this paper, we have investigated the likelihood of acknowledgment of block FIR channels in transpose shape setup for areadelay effective acknowledgment of both settled and reconfigurable applications. A summed-up piece detailing is introduced for transpose frame square FIR channel, and in light of that we have inferred transpose shape square channel for reconfigurable applications. We have exhibited a plan to distinguish the MCM obstructs for flat and vertical subexpression end in the proposed piece FIR channel for settled coefficients to diminish the computational many-sided quality. Execution correlation appears that the proposed structure includes altogether less ADP furthermore, less EPS than the current piece coordinate shape structure for medium or vast channel lengths while for the short-length channels, the current square direct-frame structure has less ADP furthermore, less EPS than the proposed structure.

# References

[1] J. G. Proakis and D. G. Manolakis, Digital Signal Processing: Principles, Algorithms and Applications. Upper Saddle River, NJ, USA: Prentice-Hall, 1996.

[2] T. Hentschel and G. Fettweis, "Software radio receivers," in CDMA Techniques for Third Generation Mobile Systems. Dordrecht, The Netherlands: Kluwer, 1999, pp. 257–283.

[3] E. Mirchandani, R. L. Zinser, Jr., and J. B. Evans, "A new adaptive noise cancellation scheme in the presence of crosstalk [speech signals]," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 39, no. 10, pp. 681–694, Oct. 1995.

[4] D. Xu and J. Chiu, "Design of a high-order FIR digital filtering and variable gain ranging seismic data acquisition system," in Proc. IEEE Southeastcon, Apr. 1993, p. 1–6.

[5] J. Mitola, Software Radio Architecture: Object-Oriented Approaches to Wireless Systems Engineering. New York, NY, USA: Wiley, 2000.

[6] S. A. White, "Applications of distributed arithmetic to digital signal processing: A tutorial review," IEEE ASSP Mag., vol. 6, no. 3, pp. 4–19, Jul. 1989.

[7] J. Park, W. Jeong, H. Mahmoodi-Meimand, Y. Wang, H. Choo, and K. Roy, "Computation sharing programmable FIR filter for low-power and high-performance applications," IEEE J. Solid State Circuits, vol. 39, no. 2, pp. 348–357, Feb. 2004.

[8] P. K. Meher, "Hardware-efficient systolization of DA-based calculation of finite digital convolution," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 8, pp. 707–711, Aug. 2006.

[9] P. K. Meher, S. Chandrasekaran, and A. Amira, "FPGA realization of FIR filters by efficient and flexible systolization using distributed arithmetic," IEEE Trans. Signal Process., vol. 56, no. 7, pp. 3009–3017, Jul. 2008.

[10] P. K. Meher, "New approach to look-up-table design and memorybased realization of FIR digital filter," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 3, pp. 592–603, Mar. 2010.

[11] R. Mahesh and A. P. Vinod, "A new common subexpression elimination algorithm for realizing low-complexity higher order digital filters," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 27, no. 2, pp. 217–219, Feb. 2008.